# **MOTOROLA Semiconductors**

# A/D AND D/A CONVERSION MANUAL

Technology and Selector Guides

1

**Data Sheets**

2

**Application Notes**

2

# ANALOG/DIGITAL AND DIGITAL/ANALOG CONVERSION MANUAL

Circuit diagrams external to Motorola products are included as a means of illustrating typical semiconductor applications; consequently complete information sufficient for construction purposes is not necessarily given. The information in this book has been carefully checked and is believed to be entirely reliable. However, no responsibility is assumed for inaccuracies. Furthermore, such information does not convey to the purchaser of the semiconductor devices described any license under the patent rights of Motorola, Inc., or others. Motorola reserves the rights to change specifications without notice.

ISBN 1870760 042

© MOTOROLA INC.,

"All rights reserved"

Revision 1984 – DLE400/D (was B001)

Reprinted 1985 – DLE400

Revised and Reprinted 1988 – DLE400RI/D

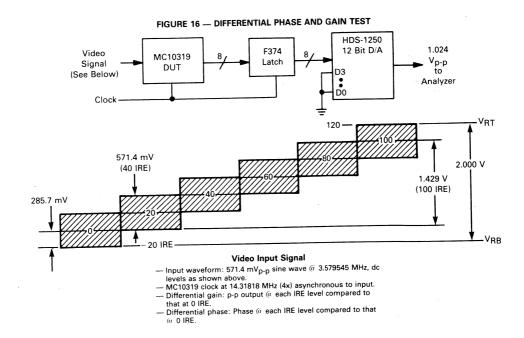

Printed in Great Britain by Hazell Watson & Viney Ltd, 2/88, 5000

# ANALOG/DIGITAL AND DIGITAL/ANALOG CONVERSION MANUAL

#### INTRODUCTION

This data conversion handbook is a compilation of data sheets and application notes from Motorola designed to help to data conversion circuit designers. It also includes a selector guide that gives the minimum technical basis on the A/D and D/A conversion.

The introduction of monolithic digital to analog conversion (DAC) IC's has opened a new area for circuit designers. The cost barriers that have in the past limited the use of the DAC to only the most sophisticated system have now been broken down.

Not only have designers found that there is a cost saving to be realized in present applications, but more important, they have found that the new economy of monolithic DAC's allows their use in numerous new applications such as microprocessor based system. As an added bonus, monolithic DAC's are superior to modular units in most performance specifications.

Motorola range of products for high speed D/A conversion include the MC1408 and the DAC08, 8-bit multiplying converters.

These circuits have broken the cost barrier that up to now caused system designers to use alternate and often less efficient techniques.

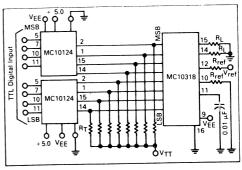

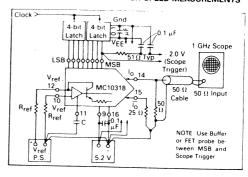

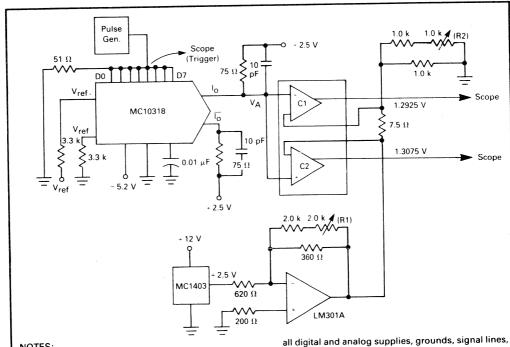

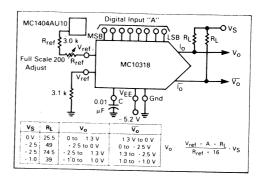

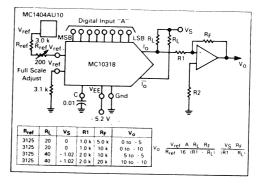

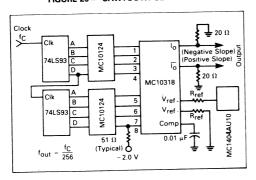

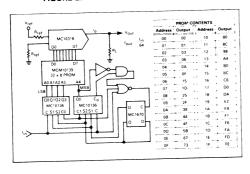

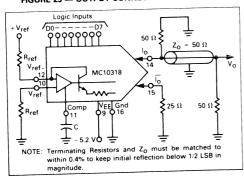

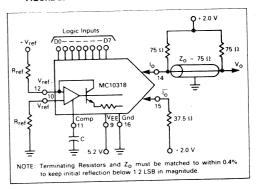

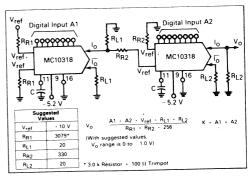

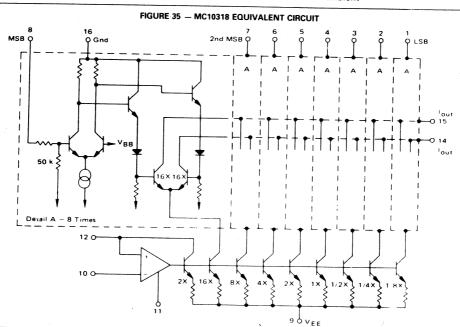

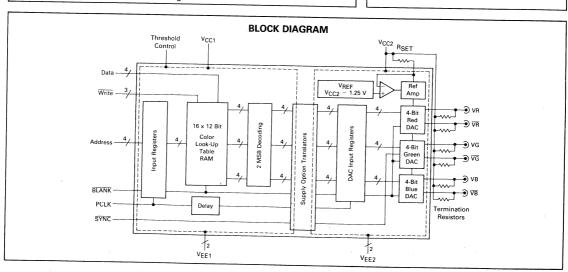

For very high speed D/A conversions, a circuit is now available: the 8-bit D/A converter MC10318 operating at speeds above 25 MHz in MECL technology. It is aimed at the video, TV, radar, storage oscilloscope and communication markets. The MC10320, a triple 4-bit color palette video DAC is also to be introduced at time of printing.

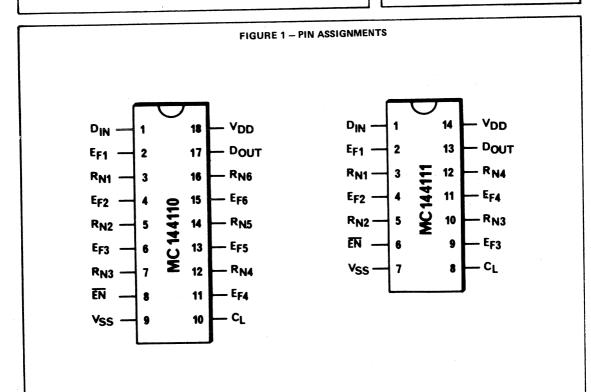

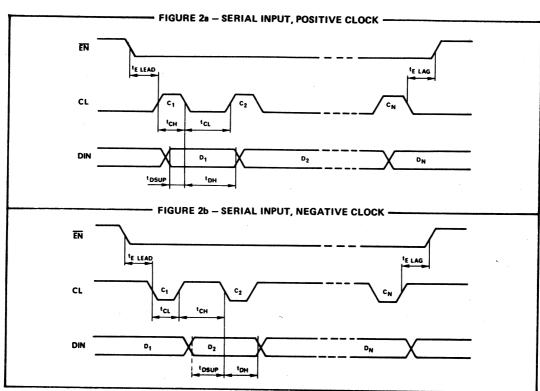

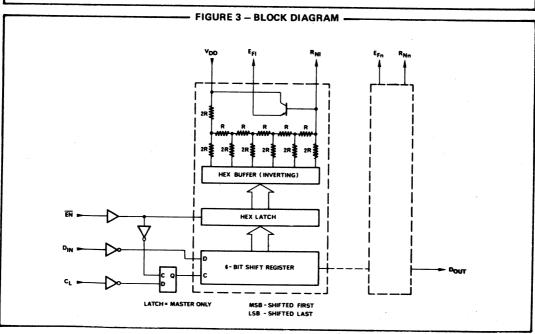

The MC144110 and MC144111 are hex and quad static D/A converters realized in CMOS technology. Each converter featuring 6-bit resolution, consists of a 6-bit shift register, 6-bit latch and a static D/A converter.

In addition, Motorola offers "building block" subsystems useful for implementation of the A/D conversion (ADC) function. These low cost devices allow the construction of high performance ADC's at a fraction of the cost of comparable modular units.

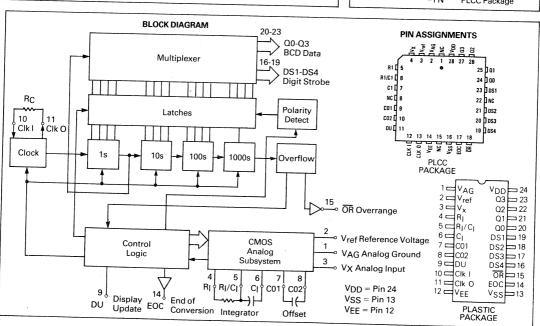

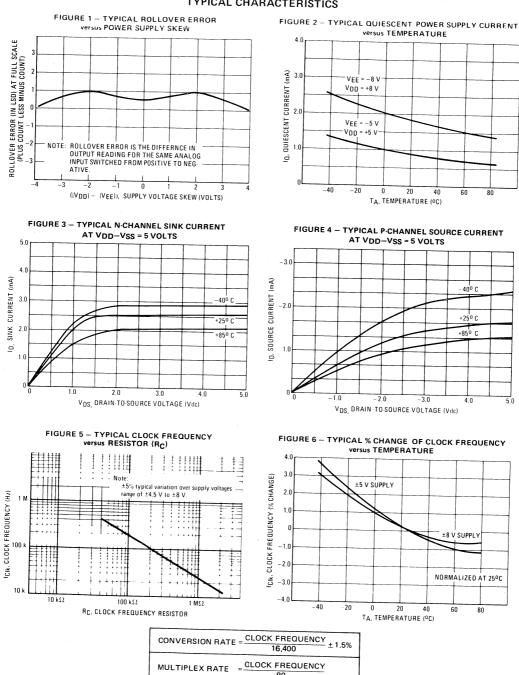

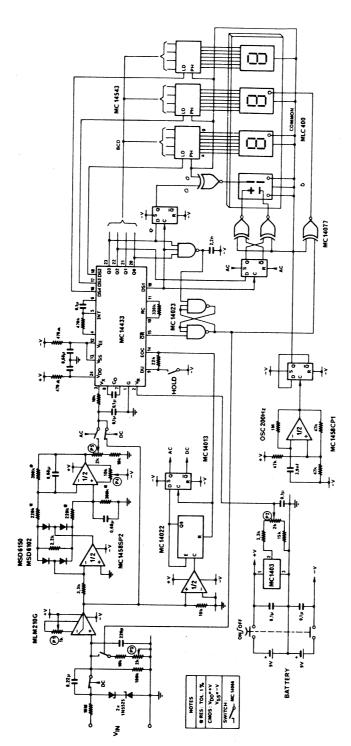

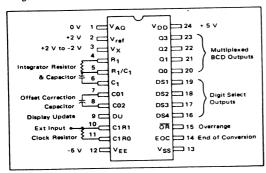

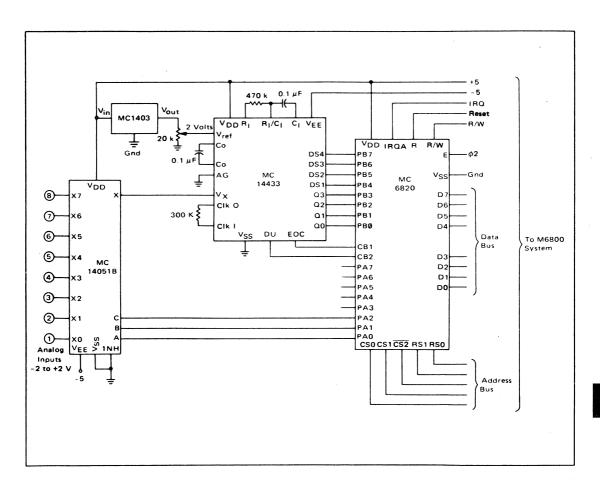

The MC14433 is a high performance, low power 3 1/2 digit A/D converter combining both linear CMOS and digital CMOS circuits on a single monolithic IC. The system forms a dual slope A/D converter with automatic zero correction and automatic polarity.

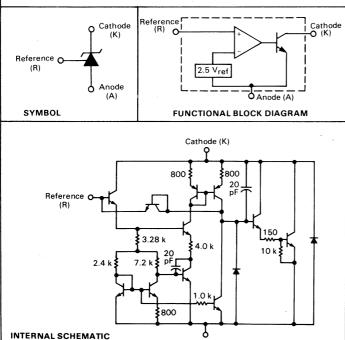

A precision band gap voltage reference for critical instrumentation and D/A converter is also available. This is the MC1503; low temperature drift is a prime design consideration. The output voltage is 2.5 V with a temperature coefficient of 10 ppm (typ).

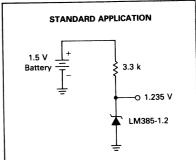

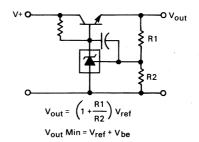

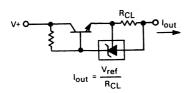

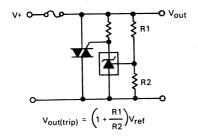

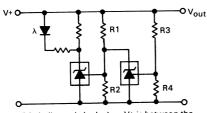

There are also the MC1504, a series available with 5.0 V, 6.25 V, 10 V output voltages and trimmable output. This voltage reference family is extended with the MC1500 series available with 2.5, 5, 6.25 and 10 V output voltages with very low temperature coefficient (5 ppm/°C typ) and the TL431 programmable precision references, and the LM385 micropower voltage reference diodes.

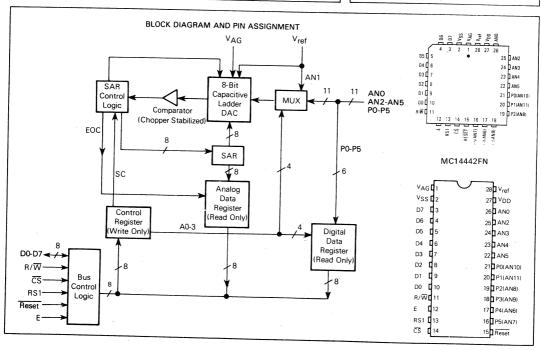

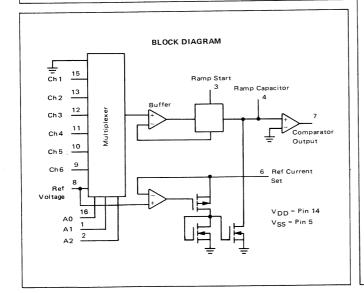

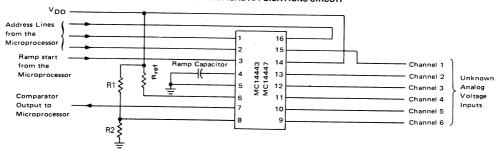

Motorola also has microprocessor based A/D Converter linear subsystem. The MC14443 and MC14447 devices are 6 channel, single slope, 8-10-bitA/D converters. Each device contains a 1 to 8 decoder, an 8 channel analog multiplexer, a buffer amplifier, a precision voltage to current converter, a ramp start circuit and a comparator.

#### **INTRODUCTION** (continued)

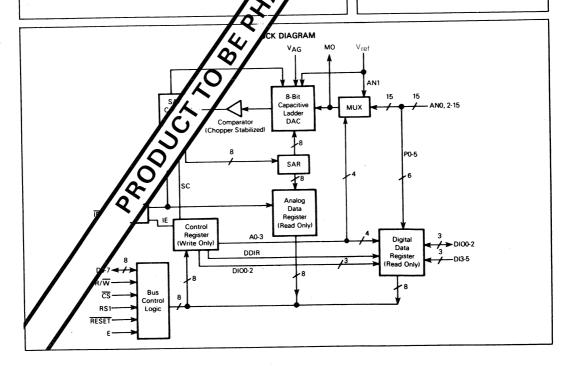

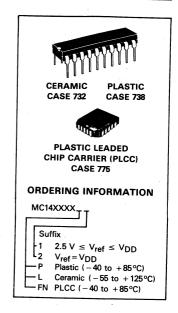

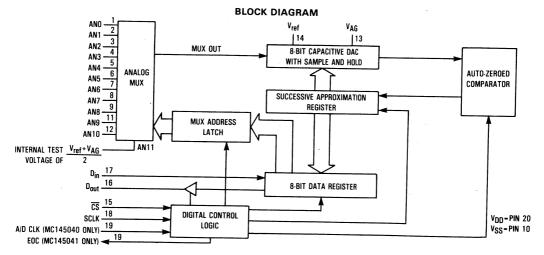

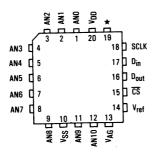

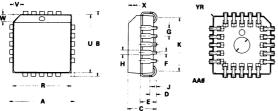

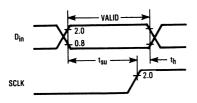

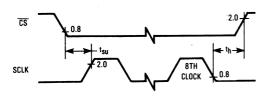

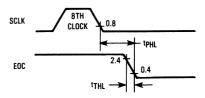

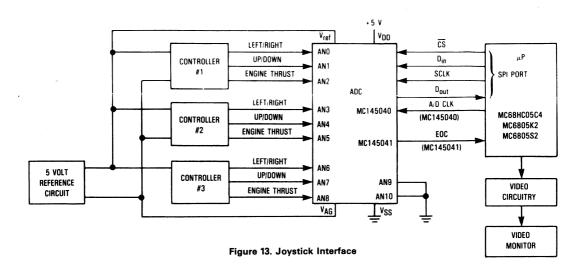

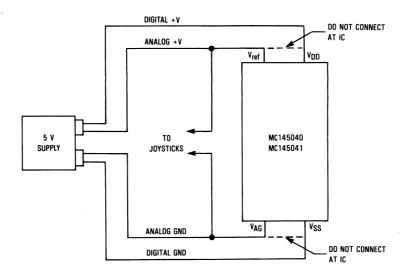

Motorola announces availability of the MC145040/MC145041 analog to digital converters with serial interface. The device are low cost 8-bit A/D converters with serial interface parts that are compatible with SPI, Microwire and other similar interfaces.

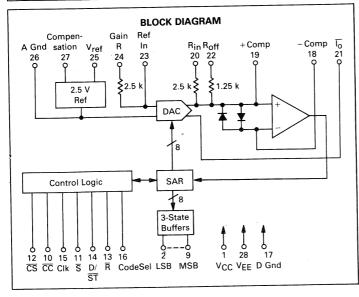

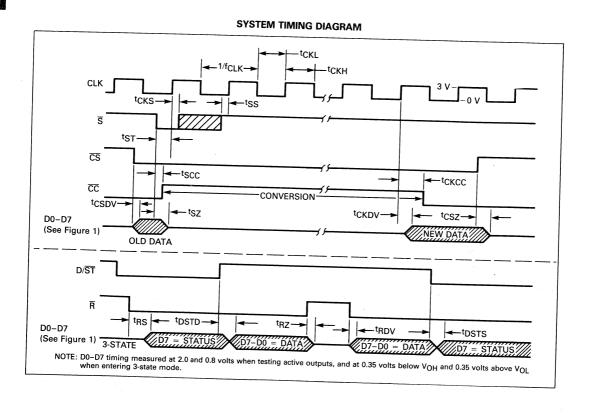

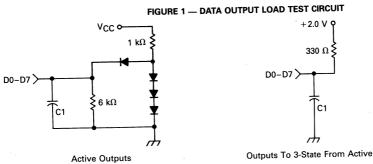

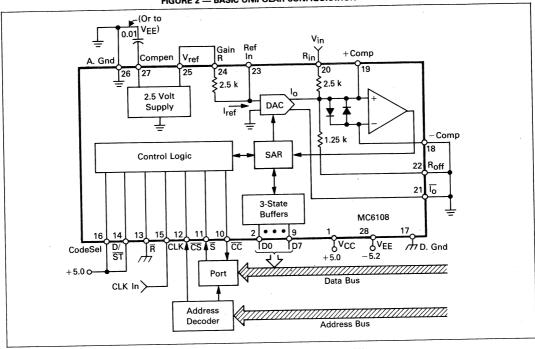

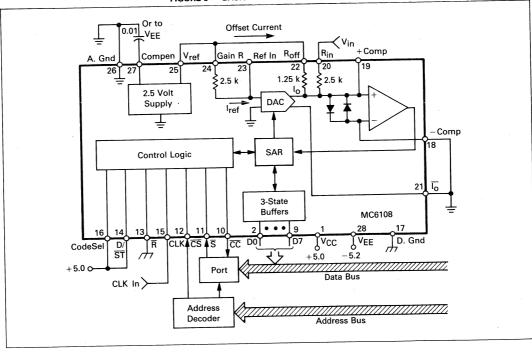

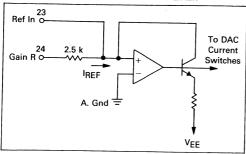

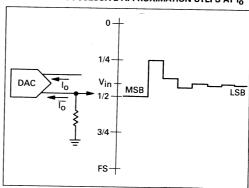

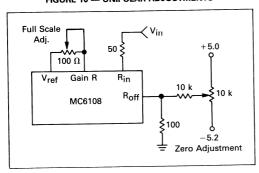

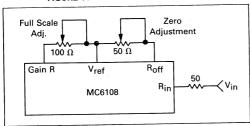

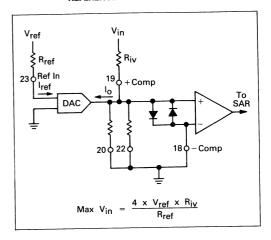

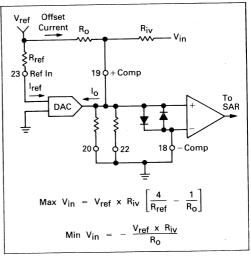

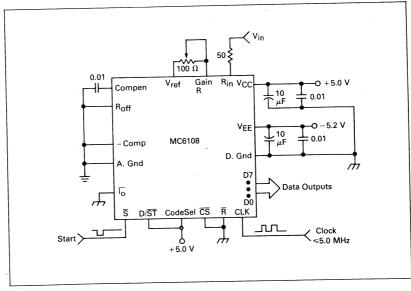

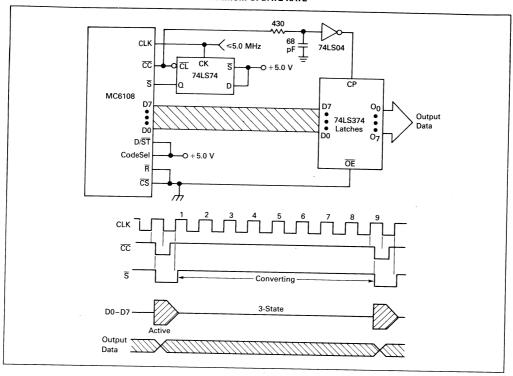

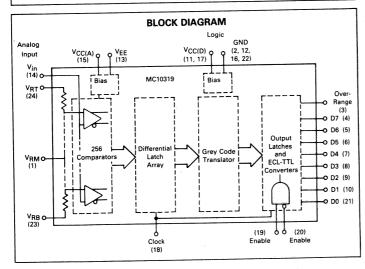

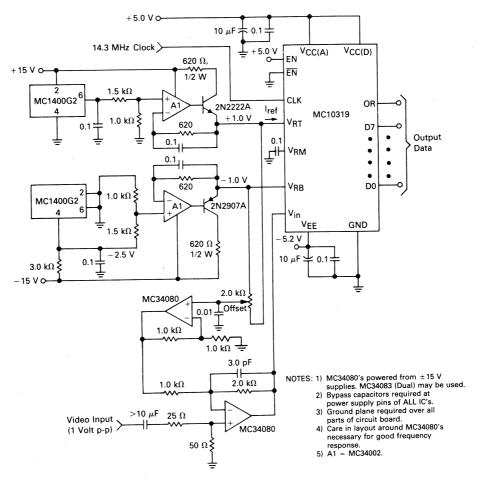

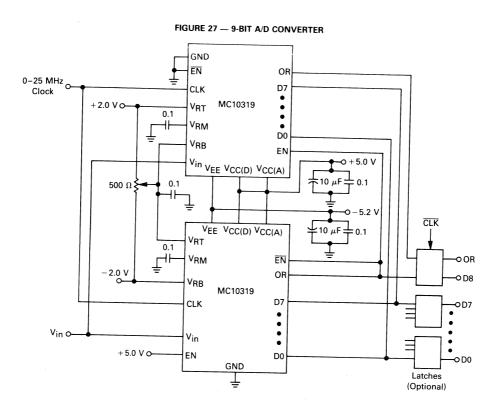

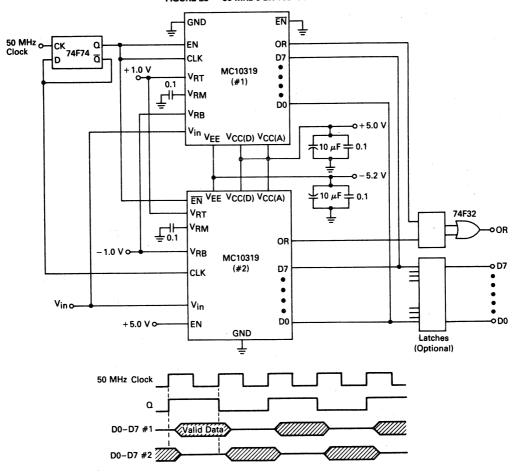

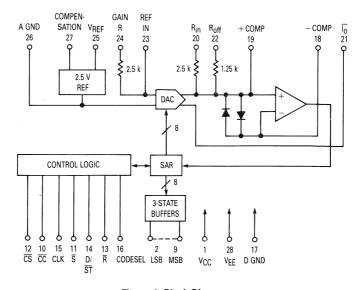

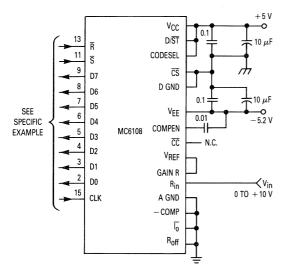

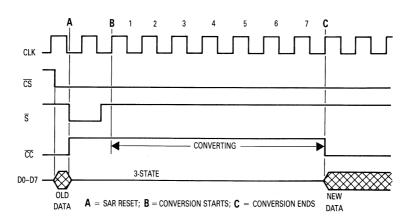

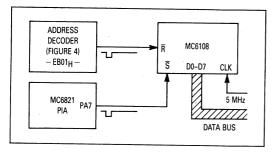

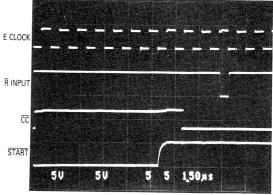

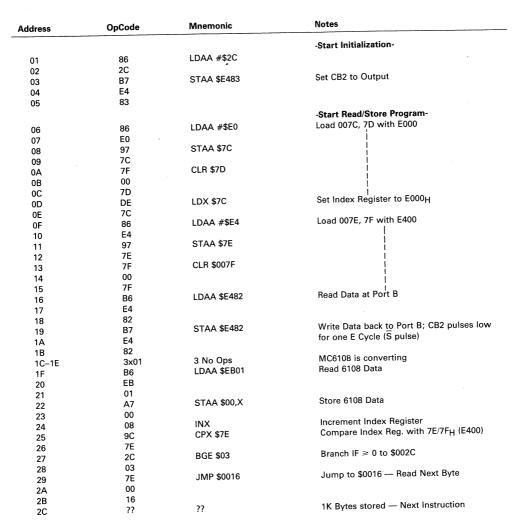

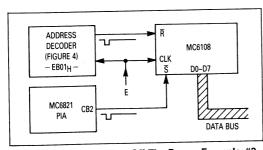

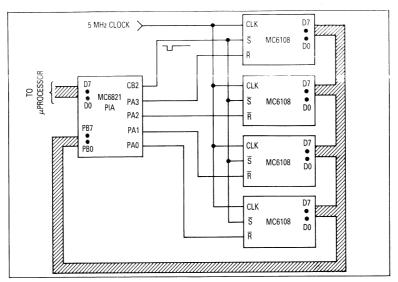

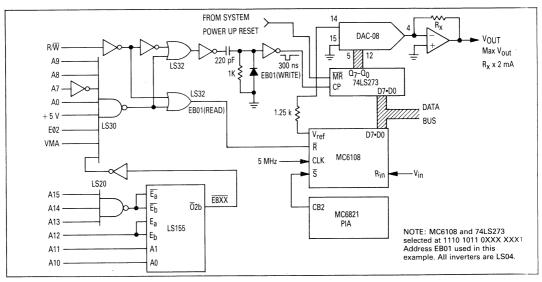

The MC10319, an 8-bit parallel high-speed flash A/D converter with overrange is now available. Applications include video display and radar processing, high-speed instrumentation, and TV broadcast video encoding. An 8-bit MPU compatible A/D converter, the MC6108, has also been introduced for use in servo control or process systems and medium speed signal processing or wave form storage.

Moreover, the MC10321, a 7-bit low cost derivative of the MC10319 for consumer-like applications, is to be introduced at time of printing.

# **TABLE OF CONTENTS**

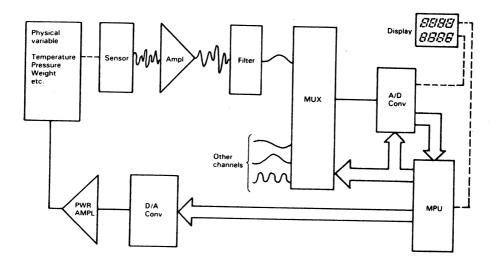

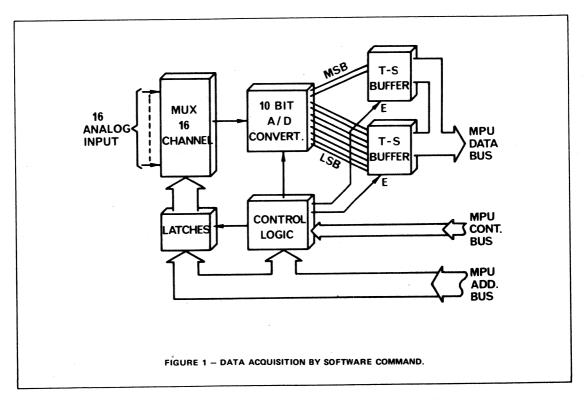

Typical Acquisition/Control System

# **SECTION 1 – TECHNOLOGY AND SELECTOR GUIDES**

|                                                                                                                                                                                                   | D/A Converters A/D Converters Voltage Reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1- 6<br>1- 9                                                                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| SECTION 2 – DATA                                                                                                                                                                                  | SHEETS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                             |

| DAC-08<br>LM285/385<br>MC1403,A/1503,A<br>MC1408/1508<br>MC6108<br>MC10318<br>MC10320<br>MC14433<br>MC14442<br>MC14443/14447<br>MC14444<br>MC144110/144111<br>MC145040/41<br>MC145042/43<br>TL431 | High Speed 8-Bit Multiplying D/A Converter Micropower Voltage Reference Diodes Precision Low-Voltage Reference 8-Bit Multiplying D/A Converter MPU Bus Compatible 8 -Bit D/A Converter High-Speed 8-Bit D/A Converter High-Speed 8-Bit flash A/D Converter Triple 4-Bit Color Palette Video D/A Converter 3 1/2 Digit A/D Converter Microprocessor-Compatible A/D Converter A/D Converter Linear Subsystem To be phased out, use MC14442 Quad & Hex D/A Converter Analog to Digital Converter with Serial Interface Similar to MC145042/43 Programmable Precision References | 2- 3<br>2- 13<br>2- 17<br>2- 21<br>2- 35<br>2- 53<br>2- 65<br>2- 84<br>2- 90<br>2-102<br>2-111<br>2-115<br>2-117<br>2-123<br>2-134<br>2-135 |

# **SECTION 3 – APPLICATION NOTES**

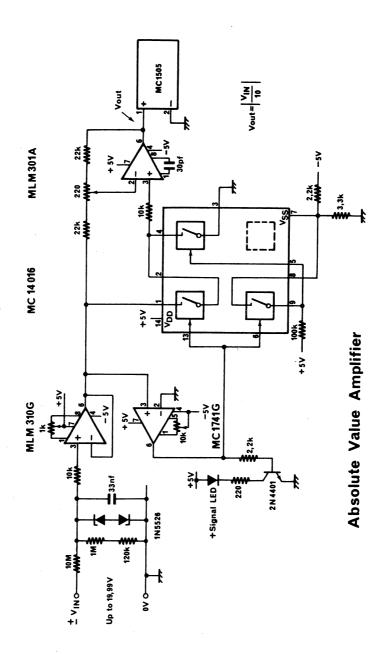

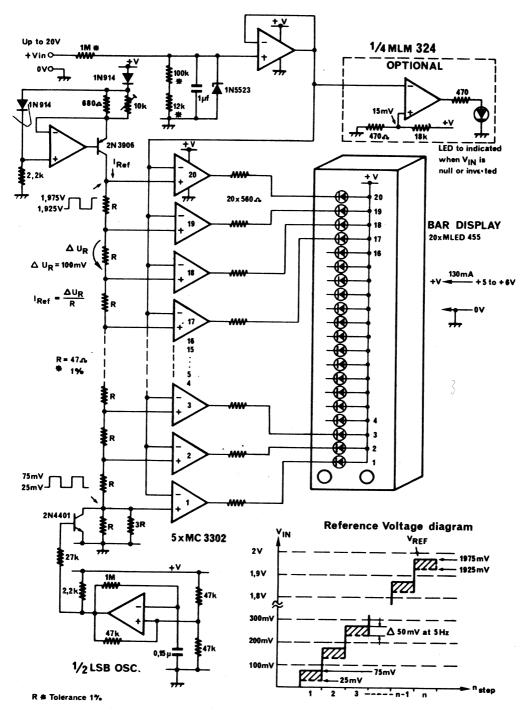

TL431

| Al-44<br>Al-48<br>Al-62 | Absolute Value Amplifier for DVM<br>AVI Analog Voltage Indicator<br>3 1/2 Digit Auto-Ranging CMOS DVM | 3- 3<br>3- 5<br>3- 7 |

|-------------------------|-------------------------------------------------------------------------------------------------------|----------------------|

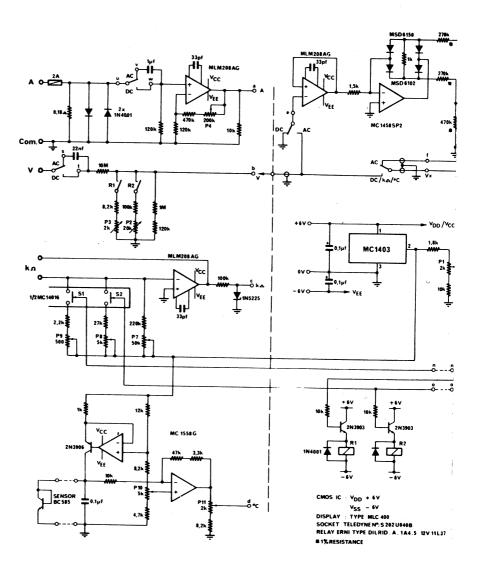

| AI-63                   | 3 1/2 Digit DMM                                                                                       | 3- 9<br>3- 13        |

| AI-73<br>AI-74          | Automatic Portable DVM Portable Digital Thermometer                                                   | 3 – 15               |

| AN321                   | The Acquisition and Recovery of Analog Signals in a M6800 Data Processing System                      | 3- 17<br>3- 27       |

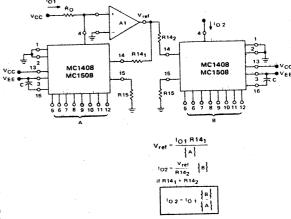

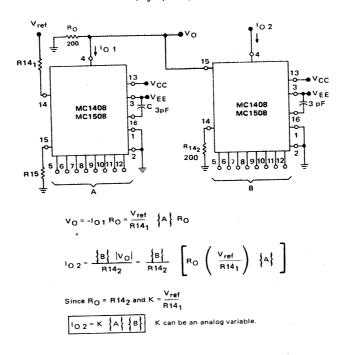

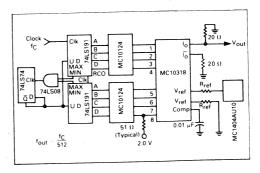

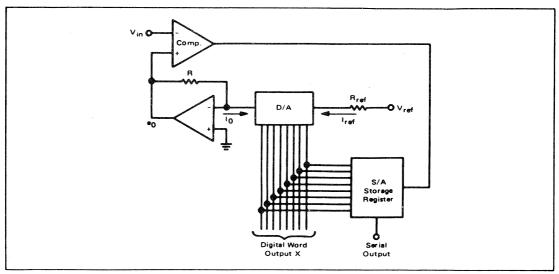

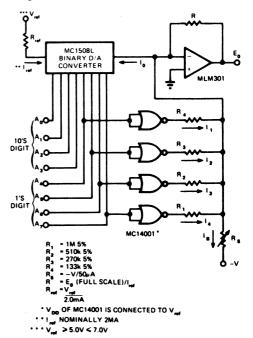

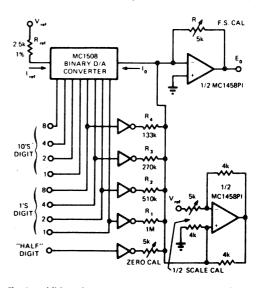

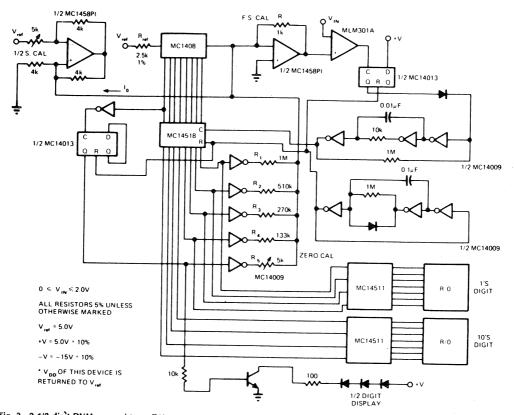

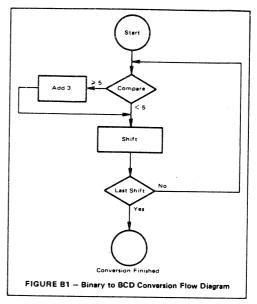

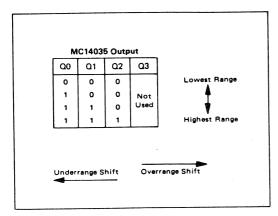

| AN702                   | High-Speed D/A and A/D Techniques Binary D/A Converters Can Provide BCD-Coded                         | 3- 21                |

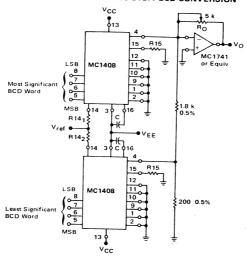

| AN713                   | Conversion                                                                                            | 3 - 42               |

# **TABLE OF CONTENTS (continued)**

# SECTION 3 - APPLICATION NOTES (continued)

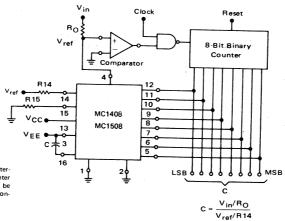

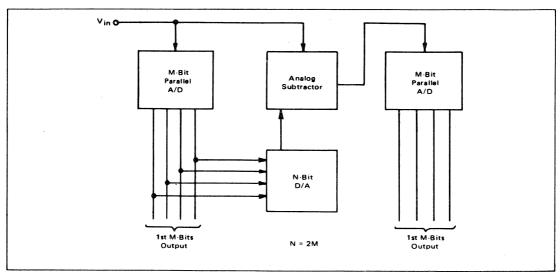

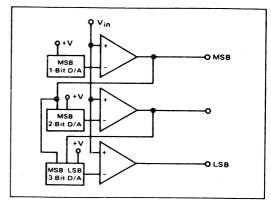

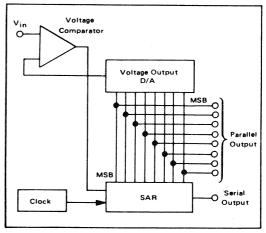

| AN716<br>AN757 | Successive Approximation A/D Conversion A/D Conversion Techniques with the | 3 -        | 47  |

|----------------|----------------------------------------------------------------------------|------------|-----|

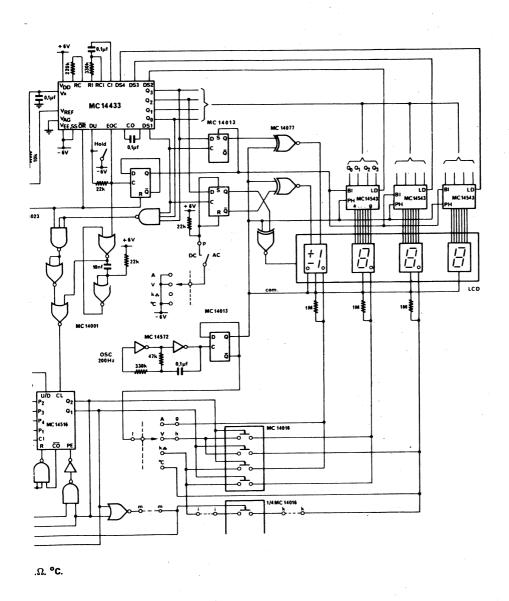

| AN769          | M6800 Microprocessor System Autoranging Digital Multimeter Using the       | 3 -        | 55  |

| AN770          | MC14433 CMOS A/D Converter  Data Acquisition Networks with NMOS and CMOS   | 3 -<br>3 - |     |

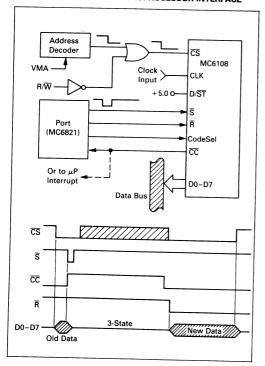

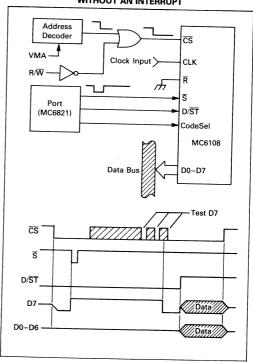

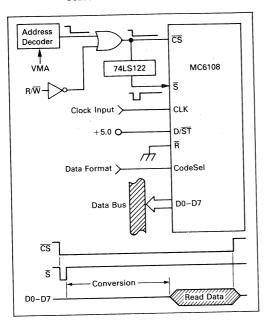

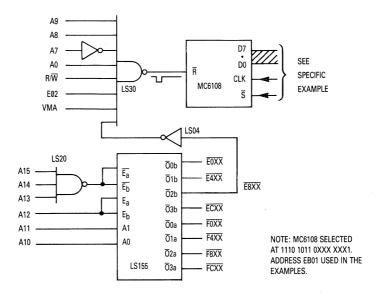

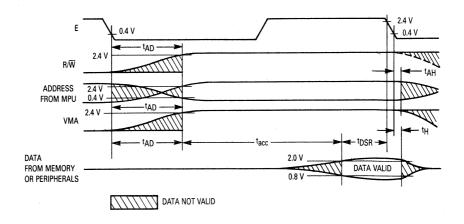

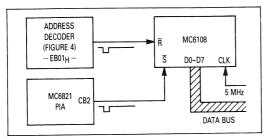

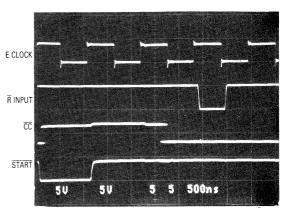

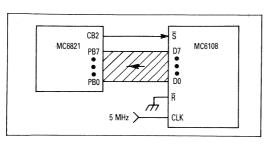

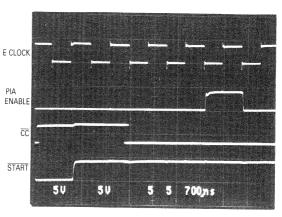

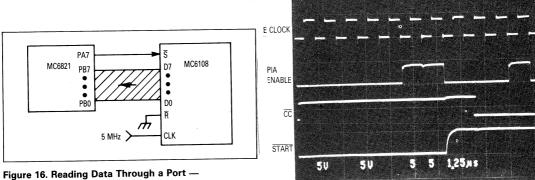

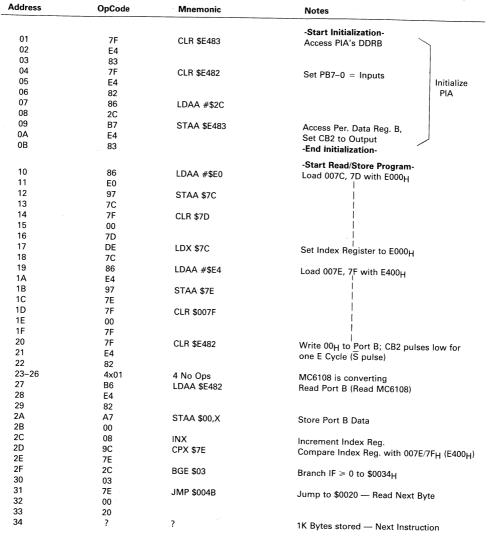

| AN963          | Interfacing the MC6108 A/D to a Microprocessor                             | 3 -        | 105 |

# Section 1 — Technology and Selector Guides

How to choose a converter - check list.

Before selecting a converter, the following questions have to be answered.

- Which resolution is needed (6, 8, 10,... bit)?

- Which accuracy is needed?

- Which linearity?

- Which logic level (input, output)?

- Which type of reference voltage, fixed, variable, internal, external?

- Which speed is necessary?

- Which settling time?

- Which power supply stability?

- Which operating temperature range is needed?

- Which is the best performance/cost ratio?

#### D/A CONVERTERS

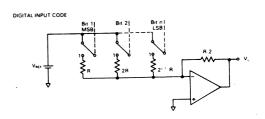

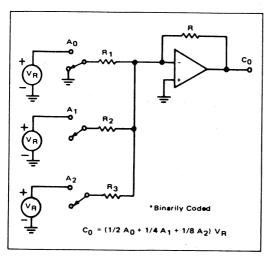

#### A - BASIC D/A CONVERTER

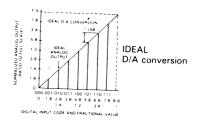

$$V_0 = -V_{REF} \left( \frac{A1}{2} + \frac{A2}{4} + \frac{A3}{8} + \dots \frac{AN}{2N} \right)$$

Where  $A_N = "1"$  if  $A_N$  is a high level  $A_N = "0"$  if  $A_N$  is a low level

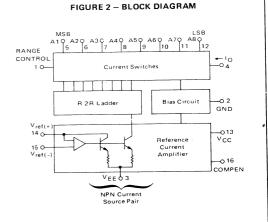

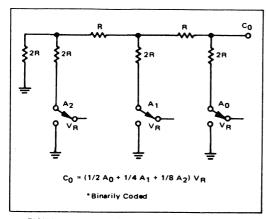

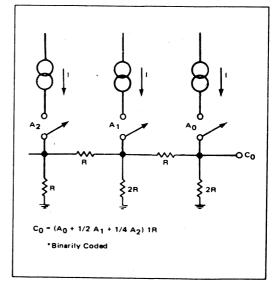

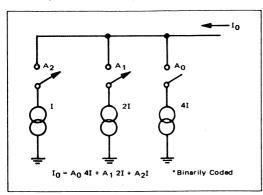

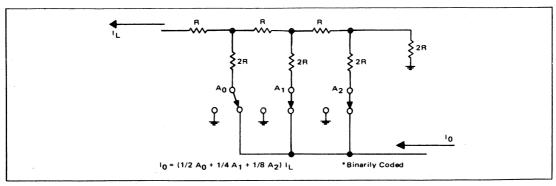

A basic D/A converter consists of a reference, a set of binary-weighted precision resistors and a set of switches. A way to reduce the resistance range is to use a limited number of repeated values with suitable attenuation - carrying this reduction of resistance values all the way, one arrives at the R-2R ladder.

#### B - D/A CONVERTER USING R-2R LADDER NETWORK

If all bits but the «MSB» are off, the output voltage is:

$$V_0 = -\frac{R}{2R} V_{REF} = -\frac{V_{REF}}{2}$$

If all bits but bit 2 are off, the output voltage is:

$$V_0 = \frac{1}{2} (-P/2R) V_{REF} = \frac{1}{4} V_{REF}$$

The lumped resistance of all the LSB circuitry (to the left of bit 2) is 2R -Since the grounded MSB series resistance, 2R, has virtually no influence, because the amplifier summing point is virtual ground, the equivalent circuit

É

#### **C - KEY PARAMETERS**

Offset error Zero error Gain error Linearity error Monotonicity Absolute accuracy

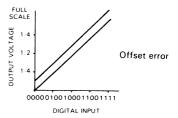

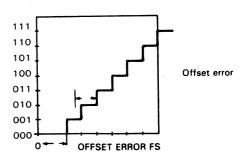

**OFFSET ERROR.** The deviation from the theoretical output with all internal D/A switches in the off state. A D/A converter that has only offset error displays a transfer function either to the right or left of the theoretical transfer function, but parallel to it.

**ZERO ERROR.** Sometimes confused with offset error because both are the same and measured at O-V. Zero error is the deviation from the theoretical output at O-V.

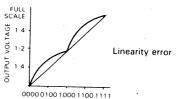

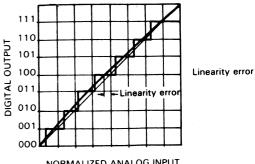

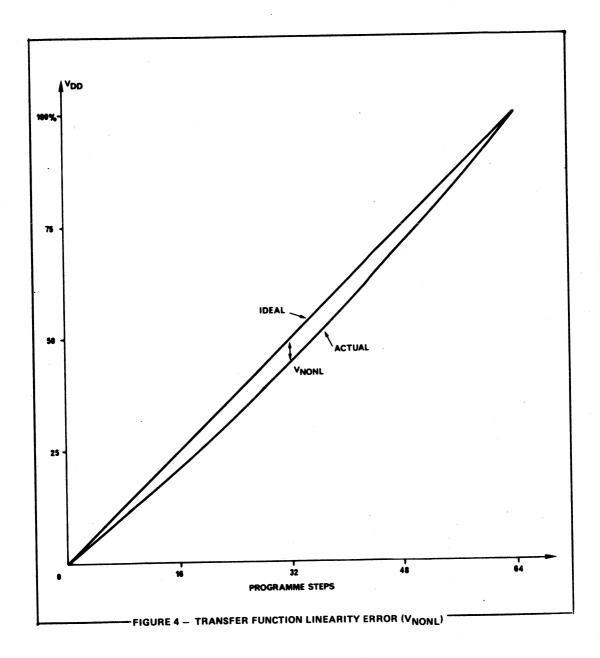

**LINEARITY ERROR** (integral linearity). A measure of how straight a device's transfer function is, it indicates the worst-case deviation of straightness of the actual transfer function from the ideal straight line. It's normally spec'd in parts of an LSB, with 1/2 = LSB maximum error the criterion for a good device.

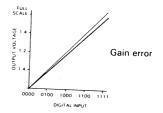

**GAIN ERROR.** The deviation of the slope of the transfer function from its ideal value. The converter's offset is first adjusted to zero. Then the difference in full scale output between the device voltage and the theoretical value is measured. Gain error is expressed as a percent of the device's output voltage.

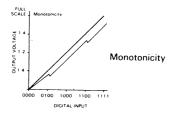

**MONOTONICITY.** This means that the analog output should increase for an increase in digital input. If the analog output decreases for an increasing input, the device is non-monotonic. Monotonicity is usually spec'd over a particular temperature range, which should at least equal the operating range. If integral linearity (see linearity error) is  $\pm$  1/2 LSB, over temperature monotonicity is guaranteed.

**ABSOLUTE ACCURACY.** The deviation of actual output voltage from ideal output voltage for a given digital input, it includes all error sources, including gain, offset and linearity. It's usually expressed as a percent of fullscale range. Relative accuracy, which often appears on spec sheets, is equivalent to integral linearity, not absolute accuracy.

# D/A CONVERTER SELECTOR GUIDE

| Reso-<br>lution<br>(bits) | Motorola<br>Part<br>Number | Max.<br>Linearity<br>in %<br>(@ 25°C) | Settling<br>Time<br>ns<br>(typ) | Inter-<br>nal<br>Refer-<br>ence | Supplies<br>(Volts) | Inputs       | Package<br>(Pins)<br>L. Ceramic<br>P: Plastic<br>D: Soic | Temp.<br>Range<br>(°C) | Function                       |

|---------------------------|----------------------------|---------------------------------------|---------------------------------|---------------------------------|---------------------|--------------|----------------------------------------------------------|------------------------|--------------------------------|

|                           | MC144110                   |                                       |                                 |                                 | 145 to 145          | смоѕ,        | 18, P                                                    | 0 to +65               | Hex static D/A                 |

| 6                         | MC144111                   | NA                                    | NA                              | No                              | +4,5 to +15         | NMOS         | 14, P                                                    | 0.00 1.00              | Quad static D/A                |

|                           | MC1408                     | 0.19                                  |                                 |                                 | + 5,                | TTL,         | 16, L, P                                                 | 0 to +70               | Multiplying                    |

| 8                         | MC1508                     | 0.19                                  | 300                             | No                              | −5 to −15           | CMOS         | 16, L                                                    | -55 to +125            |                                |

|                           | DAC-08H                    | 0.10                                  |                                 |                                 |                     |              | 16, L, P                                                 | 0 to +70               |                                |

|                           | DAC-08Q                    | 0.19                                  | 1                               |                                 | . 5 45              | TTL.<br>CMOS | 16, L                                                    | -55 to +125            | High Speed                     |

| 8                         | DAC-08E                    | 0.19                                  | 85                              | No                              | +5, -15             | ECL          | 16, L, P, D                                              | 0 to +70               | Multiplying                    |

| -                         | DAC-08C                    | 0.39                                  |                                 |                                 |                     |              | 16, L, P, D                                              | 0 to +70               |                                |

| 8                         | MC10318                    | 0.19                                  | 10                              | No                              | -5.2                | ECL          | 16, L                                                    | 0 to +70               | Very High Speed<br>Multiplying |

| 3×4                       | MC10320<br>(see Note)      | 1.56                                  | 3                               | Yes                             | +5<br>or<br>±5      | TTL,<br>ECL  | 28, L                                                    | 0 to 70                | Video DAC                      |

Note: Device to be introduced at printing date.

#### Technology and selector guide

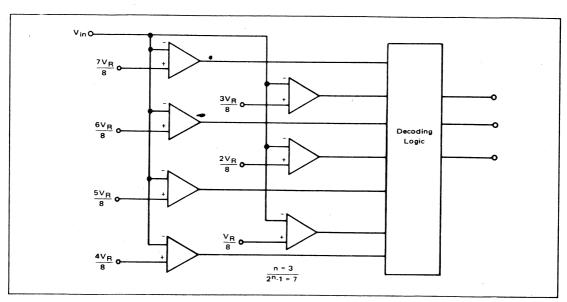

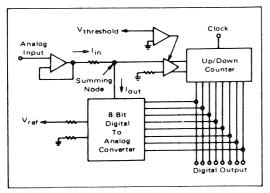

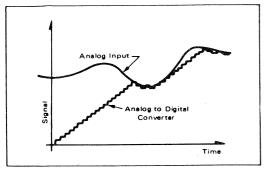

There are many techniques of A/D conversion, each having different characteristics and each favoring different applications. The dual ramp technique of A/D conversion provides an inexpensive method of obtaining high accuracy which makes it ideal for DVM applications.

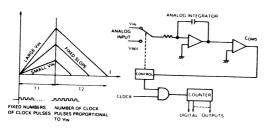

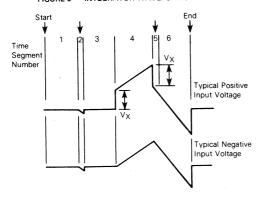

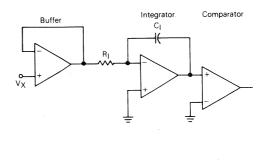

#### A - THE DUAL SLOPE TECHNIQUE - THEORY AND PRACTICE

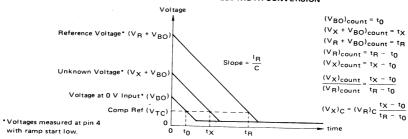

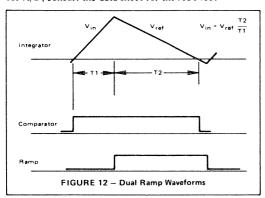

The dual ramp conversion cycle consists of two basic time periods - time period T1 results from the input unknown voltage being integrated for a fixed time interval. This integration results in the output voltage of the integrator being proportional to the input unknown voltage. At the end of the time period T1, the voltage reference (VREF) is applied to the integrator, causing the integrator output voltage to decrease. This integration continues until the output voltage again reaches the zero reference level. This time period, T2, is the down ramp time period.

Time period T1 is constant for each conversion time. The time interval T2 is dependent upon the input unknown voltage. V on capacitor is equal in T1 and T2.

$$\frac{1}{RC} \int_{T1}^{T2} V_{IN} DT = \frac{1}{RC} \int_{T2}^{T3} V_{REF} DT$$

$$T2 = T1 \frac{V_{In}}{V_{REF}} V_{IN} T1 = V_{REF} T2$$

Looking at the four variables in the relationship, T1 is a fixed time period, T2 is measured from the start of the ramp down time period until the zero level is reached and V<sub>REF</sub> is calibrated into the system. The only remaining variable in the equation is VIN, which is the analog input to be determined. Thus by counting out a time period T1, measuring the down ramp time interval T2, and calibrating the reference voltage, the dual ramp A/D conversion technique determines the value of an analog input

#### **B-KEY PARAMETERS**

Quantization error Linearity Differential non linearity Relative accuracy Gain error Gain temperature coefficient Offset error Offset temperature

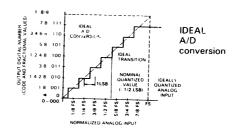

**QUANTIZATION ERROR.** This is the fundamental error associated with dividing a continuous (analog) signal into a finite number of digital bits. A 10 bit converter, for example, can only identify the input voltage to 1 part in  $2^{10}$ , and there is an unavoidable output uncertainty of  $\pm$  1/2 LSB (Least Significant Bit).

**LINEARITY.** The maximum deviation from a straight line drawn between the end points of the converter transfer function. It's usually expressed as a fraction of LSB size. A good converter has + 1/2 LSB.

**DIFFERENTIAL NON-LINEARITY.** This describes the variation in the analog value between adjacent pairs of digital numbers, over the full range of the digital output. If each transition is equal to 1 LSB, the differential non-linearity is clearly zero. If the transition is 1 LSB  $\pm$  1/2 LSB, then there is a differential linearity error of  $\pm$  1/2 LSB, but no possibility of missing codes. If the transition is 1 LSB  $\pm$  1 LDB, then there is the possibility of missing codes. This means that the output may jump from, say 011... 11 to 100... 001, missing out 100... 000.

**RELATIVE ACCURACY.** The input to output error as a fraction of full scale, with gain and offset errors adjusted to zero. Relative accuracy is a function of linearity, and is usually specified at less than  $\pm 1/2$  LSB.

**GAIN ERROR.** The difference in slope between the actual transfer function and the ideal transfer function, expressed as a percentage. This error is generally adjustable to zero by adjusting the input resistor in a current-comparing successive approximation A/D.

**OFFSET ERROR.** The mean value of input voltage required to set zero code out. This error can generally be trimmed to zero at any given temperature, or is automatically zeroed in the case of a good integrating design.

NORMALIZED ANALOG INPUT

LINEARITY ERROR

| Resolution<br>(bits) | Part     | Max.<br>Linearity<br>in %<br>(@ 25°C) | Con-<br>version<br>Time<br>(typ) | Inter-<br>nal<br>Refer-<br>ence | Supplies<br>(Volts) | Output<br>Logic<br>Levels | Package<br>(Pins)<br>L: Ceramic<br>P: Plastic<br>FN: Plastic<br>quadpack | Temp.<br>Range<br>(°C) | Function                                                                                      |

|----------------------|----------|---------------------------------------|----------------------------------|---------------------------------|---------------------|---------------------------|--------------------------------------------------------------------------|------------------------|-----------------------------------------------------------------------------------------------|

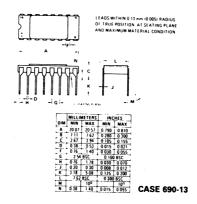

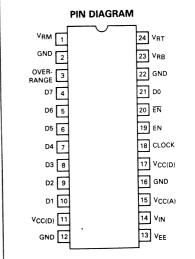

| 8                    | MC10319  | 0.19                                  | 40ns                             | No                              | -3 to -6<br>+5      | TTL                       | 24, L                                                                    | 0 to +70               | 8 bit high<br>speed A/D<br>flash<br>converter +<br>overrange bit<br>for direct 9 bit<br>stack |

| 8                    | MC6108   | 0,10                                  | 1.8μs                            | Yes                             | -5.2<br>+5          | TTL                       | 28, P                                                                    | 0 to +70               | 8 bit A/D<br>converter<br>MPU<br>compatible                                                   |

| 8                    | MC14442  | 0,19                                  | 32μs                             | No                              | 4.5 to 5.5          | TTL,<br>CMOS,<br>NMOS     | 28, P, FN                                                                | -40 to +85             | MPU bus compatible                                                                            |

| 0.40                 | MC14443  |                                       |                                  |                                 |                     | NMOS,                     |                                                                          |                        | MPU based                                                                                     |

| 8-10                 | MC14447  | 0,5                                   | 300μs                            | No                              | +4.5 to +18         | CMOS                      | 16, P                                                                    | -40  to  +85           | A/D converter linear subsystem                                                                |

| 3/2<br>digits        | MC14433  | ± 0.05                                | 40ms                             | No                              | ± 4.5 to ±8         | CMOS,<br>TTL              | 24, P, FN                                                                | -40 to +85             | 3 1/2 Digit<br>A/D converter                                                                  |

| 8                    | MC145040 | 0,19                                  | 10μs                             | No                              | 45.55               | CMOS,                     | L                                                                        | -55 to +125            | 11 channels                                                                                   |

|                      | MC145041 | 0,19                                  | 20μs                             | INO                             | 4.5 to 5.5          | TTL,<br>NMOS              | 20 P, FN                                                                 | -40 to +85             | serial data<br>interface                                                                      |

| 8                    | MC145042 |                                       | Same ac                          | MC145                           | 5040/41 but u       | .: 4b 10 4                | -11                                                                      |                        |                                                                                               |

|                      | MC145043 |                                       | d5                               | 10140                           |                     |                           | aiog inputs a                                                            | nd 28 pin pack         | age.                                                                                          |

# **VOLTAGE REFERENCE SELECTOR GUIDE**

| Out-<br>put<br>Vol-<br>tage | Motorola<br>Part<br>Number | Voltage<br>Toler-<br>ance<br>max. T <sub>A</sub><br>= 25°C | Output<br>Volt.<br>Temp.<br>Coeffic.<br>over<br>Temp.<br>Range<br>PPM/°C<br>max. | Max.<br>Output<br>Volt.<br>Change<br>over<br>Temp.<br>Range<br>mV | Line<br>Regulation<br>mV | Load<br>Regula-<br>tion<br>0≤10≤<br>10 mA<br>mV | Input<br>Voltage<br>Range (V) | Temp.<br>Range<br>Available           | Package<br>U Cera-<br>mic<br>G Metal<br>D Soic |

|-----------------------------|----------------------------|------------------------------------------------------------|----------------------------------------------------------------------------------|-------------------------------------------------------------------|--------------------------|-------------------------------------------------|-------------------------------|---------------------------------------|------------------------------------------------|

| 0.5                         | MC1403                     | . 10/                                                      | 40                                                                               | 7.0                                                               | 4.5                      | 10                                              | 4.5 to 40                     | 0 to 70                               | 8, U, D                                        |

| 2.5                         | MC1503                     | ±1%                                                        | 55                                                                               | 25                                                                | 4.5                      | 10                                              | 4.5 to 40                     | -55 to +125                           | 8, U                                           |

|                             | MC1403A                    | + 40/                                                      | 25                                                                               | 4.4                                                               | 4.5                      | 10                                              | 4.5 to 40                     | 0 to +70                              | 8, U                                           |

| 2.5                         | MC1503A                    | ±1%                                                        | 25                                                                               | 1,1                                                               | 4.5                      | 10                                              | 4.5 to 40                     | -55 to +125                           | 0, 0                                           |

| Adj.<br>2.5V to<br>36V      | TL431                      | ± 2%                                                       | 50                                                                               | 17                                                                |                          | 4                                               | 2.5 to 37                     | 0 to +70<br>-40 to +85<br>-55 to +125 | TO 92<br>8, P<br>8, U<br>8, D                  |

| 1.235V                      | 1.84005                    | 1.10/                                                      | 20                                                                               | 10                                                                |                          |                                                 | 1.25 to 40                    | 0 to +70                              | TO 92                                          |

| 2.5V                        | LM385                      | ±1%                                                        | 20                                                                               | 10                                                                |                          |                                                 | 1.23 to 40                    | -40 to +85                            | 8, D                                           |

**Section 2 — Data Sheets**

#### **DAC-08**

#### Advance Information

#### HIGH SPEED 8-BIT MULTIPLYING D-TO-A CONVERTER

The DAC-08 series is a monolithic 8-bit high speed multiplying digital-to-analog converter, capable of settling to within 1/2 LSB (0.19%) in 85 ns. Monotonic multiplying performance is retained over a wide 40-to-1 reference current range. Full scale and reference currents are matched to within 1 LSB, therefore eliminating the need for full scale trim in most applications.

Dual complementry current outputs with high voltage compliance provide added versatility and allow differential mode of operation to effectively double the peak-to-peak output swing. In many applications, output current-to-voltage conversion can be accomplished without requiring an external op amp. Noise-immune inputs permit direct interface with TTL and DTL levels when the logic threshold control, VLC, (pin 1) is grounded. All other logic family thresholds are attainable by adjusting the voltage level of pin 1. Performance characteristics are virtually unchanged over the entire ±4.5 V to ±18 V power supply range. Power consumption is typically 33 mW with ±5.0 V supplies.

The DAC-08 is available in several versions, with nonlinearity as tight as  $\pm 0.1\%~(\pm 1/4~\text{LSB})$  over temperature. All versions are guaranteed monotonic over 8 bits. For an extra margin of performance, Motorola utilizes thin-film resistors permitting very accurate resistive values which are extremely stable over temperature.

High performance characteristics, along with low cost, make the DAC-08 an excellent selection for applications such as CRT displays, waveform generation, high-speed modems, and high-speed analog-to-digital converters.

- Fast Settling Time 85 ns

- Full Scale Current Prematched to ±1 LSB

- Nonlinearity Over Temperature to ±0.1% Max

- Differential Current Outputs

- High Voltage Compliance Outputs –10 V to +18 V

- Wide Range Multiplying Capability

- Inputs Compatable With TTL, DTL, CMOS, PMOS, ECL, HTL

- Low Full Scale Current Drift

- Wide Power Supply Range ±4.5 V to ±18 V

- Low Power Consumption

- Thin-Film Resistors

- Low Cost

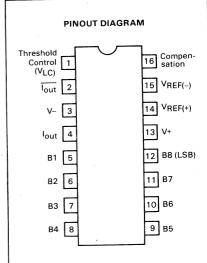

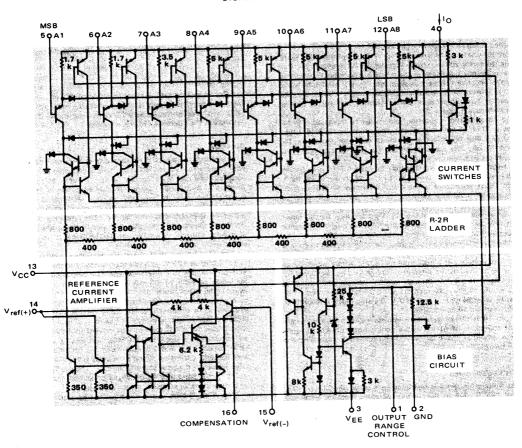

#### DAC-08 EQUIVALENT CIRCUIT (LSB) V<sub>LC</sub> B1 B2 B3 B4 B5 B6 B7 B8 Ŷ8 9 13 110 111 112 Rias Logic Buffers and Level Shifters Network lout Current VREF(+) 0 VREF(-)↔ Ref 15 2R\$ 2R\$ 2R\$ 2R\$ 2R\$ R 3 16 Compensation

#### HIGH SPEED 8-BIT MULTIPLYING D-TO-A CONVERTER

SILICON MONOLITHIC INTEGRATED CIRCUIT

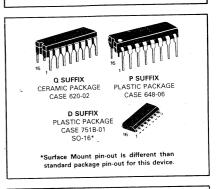

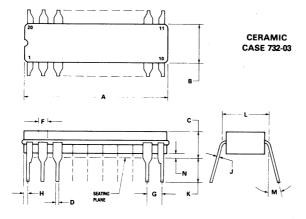

| Device   | Nonlinearity | Temperature<br>Range | Package |

|----------|--------------|----------------------|---------|

| DAC-08Q  | ± 0.19%      | -55°C to +125°C      | Ceramic |

| DAC-08HQ | ± 0.1%       | 0°C to +70°C         | Ceramic |

| DAC-08EQ | ± 0.19%      | 0°C to +70°C         | Ceramic |

| DAC-08HP | ± 0.1%       | 0°C to 70°C          | Plastic |

| DAC-08EP | ± 0.19%      | 0°C to +70°C         | Plastic |

| DAC-08CP | ± 0.39%      | 0°C to +70°C         | Plastic |

#### MAXIMUM RATINGS (T<sub>A</sub> = 25°C unless otherwise noted)

| Rating                                                              | Symbol                              | Value                   | Unit        |

|---------------------------------------------------------------------|-------------------------------------|-------------------------|-------------|

| V+ Supply to V-Supply                                               |                                     | 36                      | V           |

| Logic Inputs                                                        | _                                   | V- to V- Plus 36        | v           |

| Logic Threshold Control                                             | VLC                                 | V- to V+                | v           |

| Analog Current Outputs                                              | lout                                | See Figure 7            | mA          |

| Reference Inputs (V14, V15)                                         | VREF                                | V- to V+                | V           |

| Reference Input Differential Voltage (V14 to V15)                   | V <sub>REF(D)</sub>                 | ±18                     | V           |

| Reference Input Current (I14)                                       | IREF                                | 5.0                     | mA          |

| Operating Temperature Range<br>DAC-08 Q<br>DAC-08HQ, EQ, HP, EP, CP | TA                                  | -55 to +125<br>0 to +70 | °C          |

| Storage Temperature                                                 | TA                                  | -65 to +150             | °C          |

| Power Dissipation<br>Derate above 100°C                             | P <sub>D</sub><br>R <sub>θ</sub> JA | 500<br>10               | mW<br>mW/°C |

# ELECTRICAL CHARACTERISTICS (V<sub>S</sub> = ±15 V, I<sub>REF</sub> = 2.0 mA, T<sub>A</sub> = -55°C to +125°C, unless otherwise noted.)

|                                                                                                                                                                                                 | I                                          | T    | DAC-08              | 0 0 10 1 120        | -, umc33 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|------|---------------------|---------------------|----------|

| Characteristic                                                                                                                                                                                  | Symbol                                     | Min  |                     | Max                 | Unit     |

| Resolution                                                                                                                                                                                      |                                            | 8    | 8                   | 8                   | Bits     |

| Monotonicity                                                                                                                                                                                    | _                                          | 8    | 8                   | 8                   | Bits     |

| Nonlinearity, T <sub>A</sub> = 0°C to +70°C                                                                                                                                                     | NL                                         | _    | _                   | ±0.19               | %FS      |

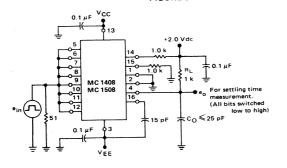

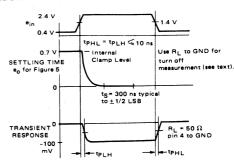

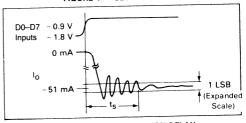

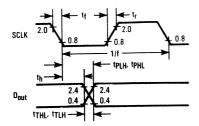

| Settling Time to ±1/2 LSB, Figure 24 (All Bits Switched On or Off, T <sub>A</sub> = 25°C, Note 1)                                                                                               | t <sub>S</sub>                             | -    | 85                  | 150                 | ns       |

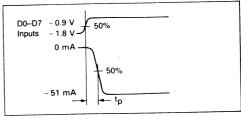

| Propagation Delay, Note 1, T <sub>A</sub> = 25°C<br>Each Bit<br>All Bits Swtiched                                                                                                               | tPLH<br>tPHL                               | _    | 35<br>35            | 60<br>60            | ns       |

| Full Scale Tempco                                                                                                                                                                               | TCIFS                                      | _    | ±10                 | ±80                 | ppm/°C   |

| Output Voltage Compliance Full Scale Current Change < 1/2 LSB, Rout > 20 megohm typ.                                                                                                            | Voc                                        | -10  | -                   | +18                 | V        |

| Full Range Current ( $V_{REF}$ = 10.000 V; R14, R15 = 5.000 k $\Omega$ , $T_{A}$ = 25°C)                                                                                                        | IFR4                                       | 1.94 | 1.99                | 2.04                | mA       |

| Full Range Symmetry (IFR4 - IFR2)                                                                                                                                                               | IFRS                                       |      | ±1.0                | ±8.0                | μА       |

| Zero Scale Current                                                                                                                                                                              | Izs                                        | _    | 0.2                 | 2.0                 | μА       |

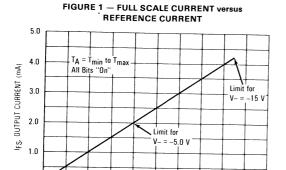

| Output Current Range<br>V- = -5.0 V<br>V- = -8.0 V to -18 V                                                                                                                                     | IOR1<br>IOR2                               | 0    | _                   | 2.1<br>4.2          | mA       |

| Logic Input Levels (V <sub>LC</sub> = 0 V)<br>Logic "0"<br>Logic "1"                                                                                                                            | V <sub>IL</sub><br>VIH                     | 2.0  | _                   | 0.8                 | ٧        |

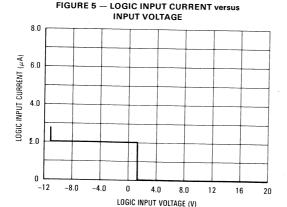

| Logic Input Current ( $V_{LC}$ = 0 V)<br>Logic Input "0" ( $V_{in}$ = -10 V to +0.8 V)<br>Logic Input "1" ( $V_{in}$ = +2.0 V to +18 V)                                                         | ηг<br>ПН                                   | _    | -2.0<br>0.002       | -10<br>10           | μΑ       |

| Logic Input Swing, V- = -15 V                                                                                                                                                                   | VIS                                        | -10  | _                   | +18                 | V        |

| Logic Threshold Range, $V_S = \pm 15 \text{ V}$                                                                                                                                                 | VTHR                                       | -10  | _                   | +13.5               | V        |

| Reference Bias Current                                                                                                                                                                          | l <sub>15</sub>                            | _    | -1.0                | -3.0                | μА       |

| Reference Input Slew Rate (Note 1) Figure 19                                                                                                                                                    | di/dt                                      | 4.0  | 8.0                 | _                   | mA/μs    |

| Power Supply Sensitivity (I <sub>REF</sub> = 1.0 mA)<br>V+ = 4.5 V to 18 V<br>V- = -4.5 V to -18 V                                                                                              | PSSI <sub>FS+</sub><br>PSSI <sub>FS-</sub> | _    | ±0.0003<br>±0.002   | ±0.01<br>±0.01      | %/%      |

| Power Supply Current VS = ±5.0 V, IREF = 1.0 mA VS = +5.0 V, -15 V, IREF = 2.0 mA                                                                                                               | +<br> -<br> +                              | _    | 2.3<br>-4.3<br>2.4  | 3.8<br>-5.8<br>3.8  | mA       |

| V <sub>S</sub> = .±15 V, I <sub>REF</sub> = 2.0 mA                                                                                                                                              | -<br> +<br> -                              | =    | -6.4<br>2.5<br>-6.5 | -7.8<br>3.8<br>-7.8 |          |

| Power Dissipation $V_S = \pm 5.0 \text{ V, } I_{REF} = 1.0 \text{ mA}$ $V_S = \pm 5.0 \text{ V, } -15 \text{ V, } I_{REF} = 2.0 \text{ mA}$ $V_S = \pm 15 \text{ V, } I_{REF} = 2.0 \text{ mA}$ | P <sub>D</sub>                             | =    | 33<br>108<br>135    | 48<br>136<br>174    | mW       |

Note 1. Parameter is not 100% tested; guaranteed by design.

ELECTRICAL CHARACTERISTICS (V<sub>S</sub> = ±15 V, I<sub>REF</sub> = 2.0 mA, T<sub>A</sub> = 0°C to 70°C, unless otherwise noted.)

| ELECTRICAL CHARACTERISTIC                                                                                                                                                           |                        | D/                | AC-08H              |                     | DA                | C-08E               |                     | DA                | 1                   |                     |        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-------------------|---------------------|---------------------|-------------------|---------------------|---------------------|-------------------|---------------------|---------------------|--------|

| Characteristic                                                                                                                                                                      | Symbol                 | Min               | Тур                 | Max                 | Min               | Тур                 | Max                 | Min               | Тур                 | Max                 | Unit   |

| Resolution                                                                                                                                                                          |                        | 8                 | 8                   | 8                   | 8                 | 8                   | 8                   | 8                 | 8                   | 8                   | Bits   |

| Monotonicity                                                                                                                                                                        |                        | 8                 | 8                   | 8                   | 8                 | 8                   | 8                   | 8                 | 8                   | 8                   | Bits   |

| Nonlinearity, T <sub>A</sub> = 0°C to +70°C                                                                                                                                         | NL                     |                   |                     | ±0.1                |                   |                     | ±0.19               | _                 | _                   | ±0.39               | %FS    |

| Settling Time to ±1/2 LSB  (All Bits Switched On or Off,  TA = 25°C, Note 1) Figure 24                                                                                              | t <sub>s</sub>         | _                 | 85                  | 135                 | _                 | 85                  | 150                 | -                 | 85                  | 150                 | ns     |

| Propagation Delay, Note 1, T <sub>A</sub> = 25°C<br>Each Bit<br>All Bits Swtiched                                                                                                   | tPLH<br>tPHL           | _                 | 35<br>35            | 60<br>60            | _                 | 35<br>35            | 60<br>60            | _                 | 35<br>35            | 60<br>60            | ns     |

| Full Scale Tempco                                                                                                                                                                   | TCIFS                  | _                 | ±10                 | ±50                 |                   | ±10                 | ±50                 |                   | ±10                 | ±80                 | ppm/°C |

| Output Voltage Compliance Full Scale Current Change < 1/2 LSB, Rout > 20 megohm typ.                                                                                                | Voc                    | -10               |                     | +18                 | -10               |                     | +18                 | -10               |                     | +18                 | ٧      |

| Full Range Current (VREF = 10.000 V; R14, R15 = 5.000 k $\Omega$ ) TA = 25°C                                                                                                        | IFR4                   | 1.984             | 1.992               | 2.000               | 1.94              | 1.99                | 2.04                | 1.94              | 1.99                | 2.04                | mA     |

| Full Range Symmetry (IFR4 - IFR2)                                                                                                                                                   | IFRS                   | _                 | ±0.5                | ±4.0                |                   | ±1.0                | ±8.0                |                   | ±2.0                | ±16.0               | μΑ     |

| Zero Scale Current                                                                                                                                                                  | Izs                    |                   | 0.1                 | 1.0                 |                   | 0.2                 | 2.0                 |                   | 0.2                 | 4.0                 | μΑ     |

| Output Current Range<br>V- = -5.0 V<br>V- = -8.0 V to -18 V                                                                                                                         | IOR1<br>IOR2           | 0                 | _                   | 2.1<br>4.2          | 0                 | _                   | 2.1<br>4.2          | 0<br>0            | _                   | 2.1<br>4.2          | mA     |

| Logic Input Levels (V <sub>LC</sub> = 0 V)<br>Logic "0"<br>Logic "1"                                                                                                                | V <sub>IL</sub><br>VIH | <br>2.0           | =                   | 0.8                 | _<br>2.0          | _                   | 0.8                 | _<br>2.0          | _                   | 0.8                 | V      |

| Logic Input Current (V <sub>LC</sub> = 0 V) Logic Input "0" (Vin = -10 V to +0.8 V) Logic Input "1" (Vin = +2.0 V to +18 V)                                                         | , lit                  | <u>-</u>          | -2.0<br>0.002       | -10<br>10           | _<br>_            | -2.0<br>0.002       | -10<br>10           | <u> </u>          | -2.0<br>0.002       | -10<br>10           | μΑ     |

| Logic Input Swing, V- = -15 V                                                                                                                                                       | VIS                    | . –10             | . —                 | +18                 | -10               | _                   | +18                 | -10               |                     | +18                 | V      |

| Logic Threshold Range, V <sub>S</sub> = ±15 V                                                                                                                                       | VTHR                   | -10               |                     | +13.5               | -10               |                     | +13.5               | -10               |                     | +13.5               | V      |

| Reference Bias Current                                                                                                                                                              | 115                    |                   | -1.0                | -3.0                | _                 | -1.0                | -3.0                |                   | -1.0                | -3.0                | μΑ     |

| Reference Input Slew Rate<br>(Note 1) Figure 19                                                                                                                                     | dl/dt                  | 4.0               | 8.0                 | _                   | 4.0               | 8.0                 | _                   | 4.0               | 8.0                 | _                   | mA/μs  |

| Power Supply Sensitivity (I <sub>REF</sub> = 1.0 mA) V+ = 4.5 V to 18 V V- = -4.5 V to -18 V                                                                                        | PSSIFS+<br>PSSIFS-     | ±0.0003<br>±0.002 | ±0.01<br>±0.01      | _                   | ±0.0003<br>±0.002 | ±0.01<br>±0.01      |                     | ±0.0003<br>±0.002 | ±0.01<br>±0.01      | _                   | %/%    |

| Power Supply Current<br>V <sub>S</sub> = ±5.0 V, I <sub>REF</sub> = 1.0 mA                                                                                                          | +<br> -                | _                 | 2.3<br>-4.3<br>2.4  | 3.8<br>-5.8<br>3.8  |                   | 2.3<br>-4.3<br>2.4  | 3.8<br>-5.8<br>3.8  | _ ·               | 2.3<br>-4.3<br>2.4  | 3.8<br>-5:8<br>3.8  | mA     |

| $V_S = +5.0 \text{ V}, -15 \text{ V}, I_{REF} = 2.0 \text{ mA}$<br>$V_S = \pm 15 \text{ V}, I_{REF} = 2.0 \text{ mA}$                                                               | -<br> -<br> +<br> -    | _<br>_<br>_       | -6.4<br>2.5<br>-6.5 | -7.8<br>3.8<br>-7.8 |                   | -6.4<br>2.5<br>-6.5 | -7.8<br>3.8<br>-7.8 | _<br>             | -6.4<br>2.5<br>-6.5 | -7.8<br>3.8<br>-7.8 |        |

| Power Dissipation  V <sub>S</sub> = ±5.0 V, I <sub>REF</sub> = 1.0 mA  V <sub>S</sub> = +5.0 V, -15 V, I <sub>REF</sub> = 2.0 mA  V <sub>S</sub> = ±15 V, I <sub>REF</sub> = 2.0 mA | PD                     | _                 | 33<br>108<br>135    | 48<br>136<br>174    | _<br>             | 33<br>108<br>135    | 48<br>136<br>174    |                   | 33<br>108<br>135    | 48<br>136<br>174    | mW     |

V<sub>S</sub> = ±15 V, I<sub>REF</sub> = 2.0 mA

Note 1. Parameter is not 100% tested; guaranteed by design.

0

0

1.0

## 9

#### TYPICAL PERFORMANCE CURVES

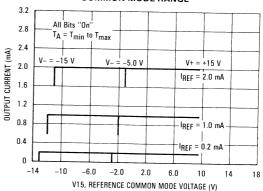

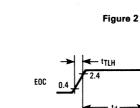

#### FIGURE 2 — REFERENCE AMP COMMON MODE RANGE

NOTE: Positive Common Mode Range is Always (V+) -1.5 V

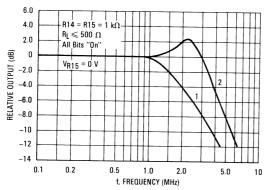

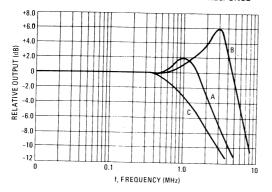

FIGURE 3 — REFERENCE INPUT FREQUENCY RESPONSE

IREF, REFERENCE CURRENT (mA)

3.0

4.0

5.0

2.0

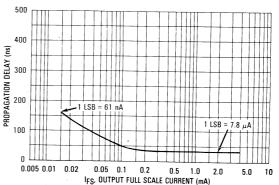

FIGURE 4 -- LSB PROPAGATION DELAY versus IFS

Curve 1 —  $C_C$  = 15 pF,  $V_{in}$  = 2.0 V p-p Centered at +1.0 V (Large-Signal) Curve 2 —  $C_C$  = 15 pF,  $V_{in}$  = 50 mV p-p Centered at +200 mV (Small-Signal)

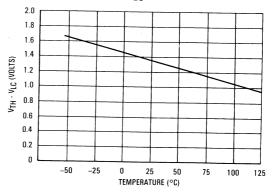

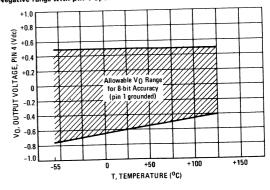

FIGURE 6 — V<sub>TH</sub> - V<sub>LC</sub> versus TEMPERATURE

#### TYPICAL PERFORMANCE CURVES

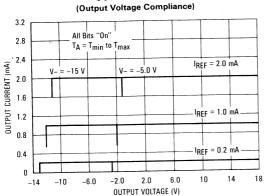

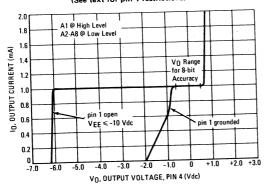

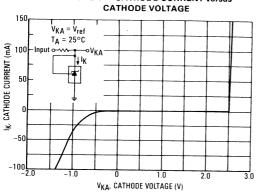

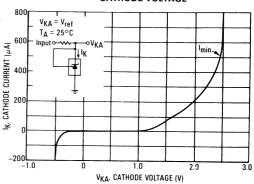

# FIGURE 7 — OUTPUT CURRENT versus OUTPUT VOLTAGE

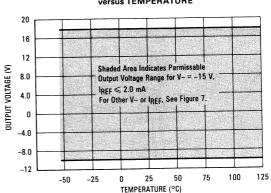

# FIGURE 8 — OUTPUT VOLTAGE COMPLIANCE versus TEMPERATURE

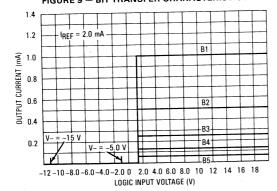

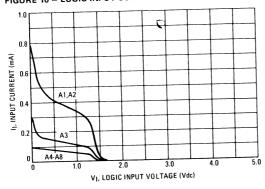

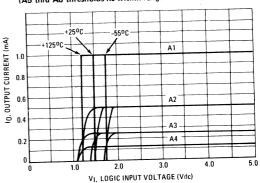

#### FIGURE 9 — BIT TRANSFER CHARACTERISTICS

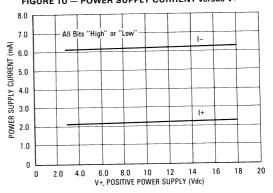

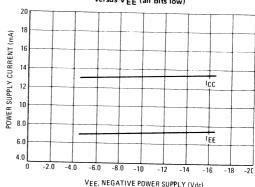

FIGURE 10 — POWER SUPPLY CURRENT versus V+

NOTE: B1-B8 have identical transfer characteristics. Bits are fully switched with less than 1/2 LSB error, at less than  $\pm 100$  mV from actual threshold. These switching points are guaranteed to lie between 0.8 V and 2.0 V over operating temperature range (VLC = 0 V).

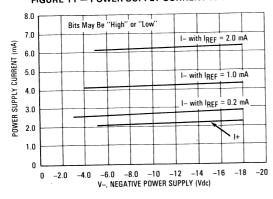

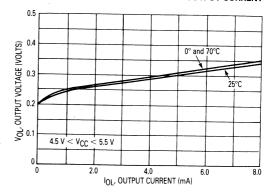

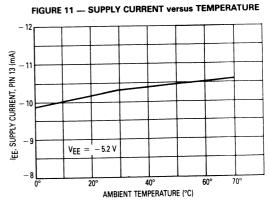

#### FIGURE 11 — POWER SUPPLY CURRENT versus V-

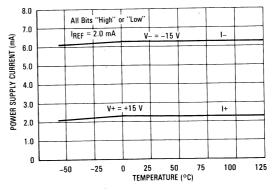

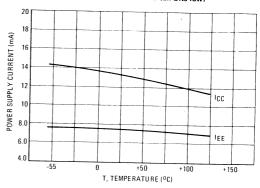

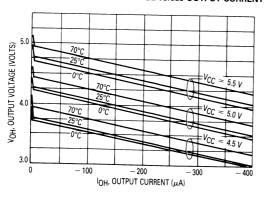

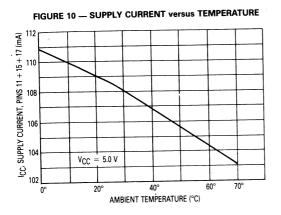

# FIGURE 12 — POWER SUPPLY CURRENT versus TEMPERATURE

## 2

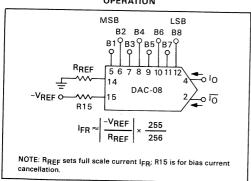

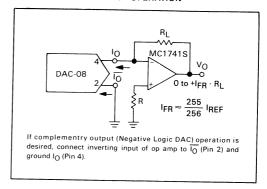

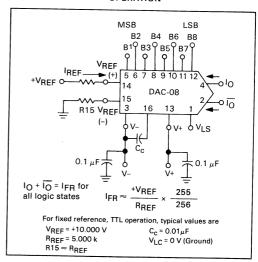

#### **BASIC CIRCUIT CONFIGURATIONS**

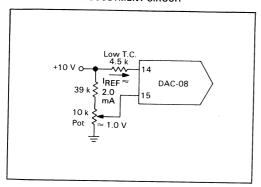

FIGURE 13 — RECOMMENDED FULL SCALE

ADJUSTMENT CIRCUIT

FIGURE 15 — NEGATIVE LOW IMPEDANCE OUTPUT OPERATION

FIGURE 17 — BASIC NEGATIVE REFERENCE OPERATION

FIGURE 14 — POSITIVE LOW IMPEDANCE OUTPUT OPERATION

FIGURE 16 — BASIC POSITIVE REFERENCE OPERATION

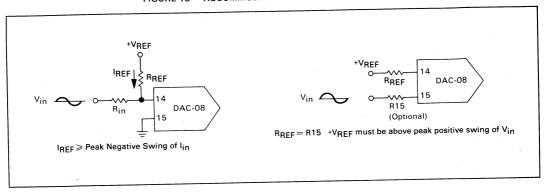

#### BASIC CIRCUIT CONFIGURATIONS

#### FIGURE 18 — ACCOMMODATING BIPOLAR REFERENCES

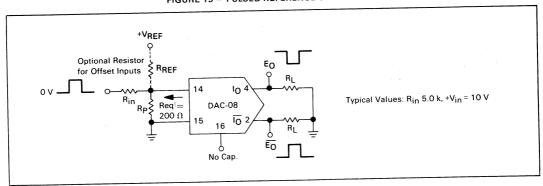

#### FIGURE 19 — PULSED REFERENCE OPERATION

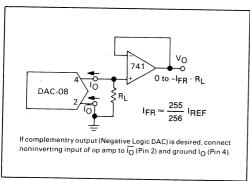

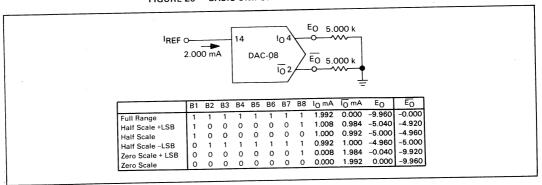

FIGURE 20 — BASIC UNIPOLAR NEGATIVE OPERATION

#### **BASIC CIRCUIT CONFIGURATIONS**

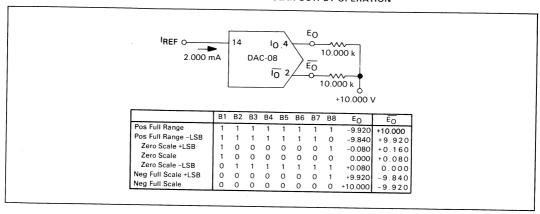

FIGURE 21 — BASIC BIPOLAR OUTPUT OPERATION

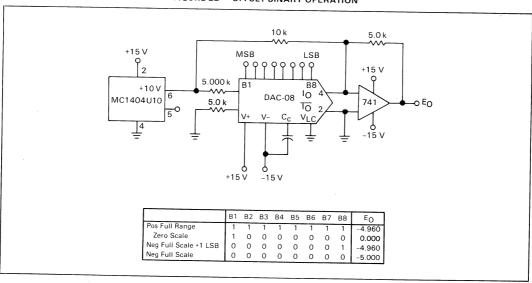

FIGURE 22 — OFFSET BINARY OPERATION

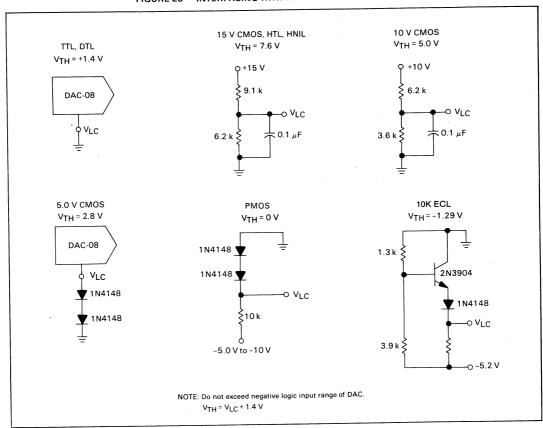

FIGURE 23 — INTERFACING WITH VARIOUS LOGIC FAMILIES

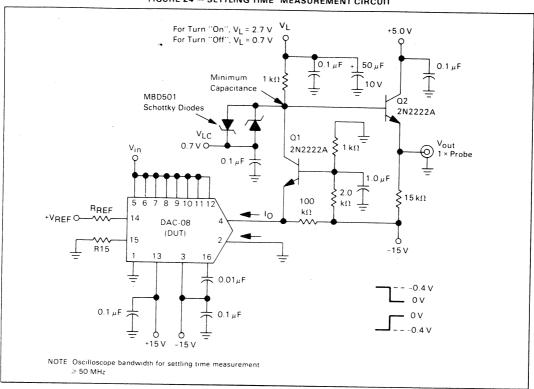

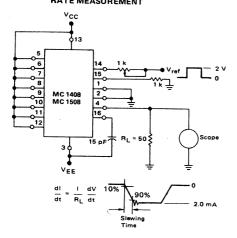

FIGURE 24 — SETTLING TIME MEASUREMENT CIRCUIT

### LM285 LM385

#### MICROPOWER VOLTAGE REFERENCE DIODES

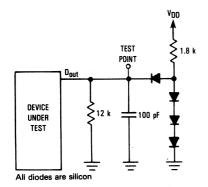

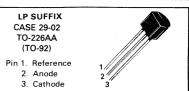

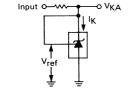

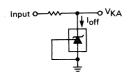

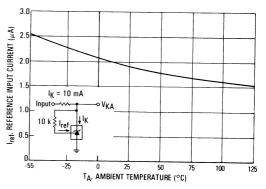

The LM285/LM385 series are micropower two-terminal bandgap voltage regulator diodes. Designed to operate over a wide current range of 10  $\mu A$  to 20 mA, these devices feature exceptionally low dynamic impedance, low noise and stable operation over time and temperature. Tight voltage tolerances are achieved by on-chip trimming. The large dynamic operating range enables these devices to be used in applications with widely varying supplies with excellent regulation. Extremely low operating current make these devices ideal for micropower circuitry like portable instrumentation, regulators and other analog circuitry where extended battery life is required.

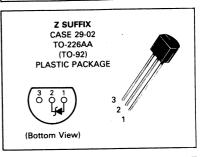

The LM285/LM385 series are packaged in a low cost TO-226AA (TO-92) plastic case and are available in two voltage versions of 1.235 and 2.500 volts as denoted by the device suffix (see ordering information table). The LM285 is specified over a  $-40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$  temperature range while the LM385 is rated from  $0^{\circ}\text{C}$  to  $+70^{\circ}\text{C}$ .

- Operating Current from 10 μA to 20 mA

- 1.0%, 1.5%, 2.0% and 3.0% Initial Tolerance Grades

- Low Temperature Coefficient

- 1.0 Ω Dynamic Impedance

- Available in 1.235 and 2.500 Volt Versions

# EQUIVALENT CIRCUIT SCHEMATIC 2 8.0 Ω Open for 1.235 V Open for 2.5 V 425 k 10 k 10 k

# MICROPOWER VOLTAGE REFERENCE DIODES

SILICON MONOLITHIC INTEGRATED CIRCUIT

| ORDERING INFORMATION |                    |                                      |           |  |  |  |  |  |

|----------------------|--------------------|--------------------------------------|-----------|--|--|--|--|--|

| Device               | Temp.<br>Range     | Reverse<br>Break-<br>down<br>Voltage | Tolerance |  |  |  |  |  |

| LM285Z-1.2           | -40 °C<br>to +85°C | 1.235<br>Volts                       | ± 1.0%    |  |  |  |  |  |

| LM285Z-2.5           |                    | 2.500<br>Volts                       | ± 1.5%    |  |  |  |  |  |

| LM385BZ-1.2          | 0°C to<br>+70°C    | 1.235<br>Volts                       | ±1.0%     |  |  |  |  |  |

| LM385Z-1.2           |                    | 1.235<br>Volts                       | ± 2.0%    |  |  |  |  |  |

| LM385BZ-2.5          |                    | 2.500<br>Volts                       | ± 1.5%    |  |  |  |  |  |

| LM385Z-2.5           |                    | 2.500<br>Volts                       | ± 3.0%    |  |  |  |  |  |

DS9633

#### **MAXIMUM RATINGS** $(T_A = +25^{\circ}C \text{ unless otherwise noted})$

| Rating                                                | Symbol           | Value                   | Unit<br>mA |  |

|-------------------------------------------------------|------------------|-------------------------|------------|--|

| Reverse Current                                       | l <sub>B</sub>   | 30                      |            |  |

| Forward Current                                       | le<br>''         | 10                      | mA         |  |

| Operating Ambient Temperature Range<br>LM285<br>LM385 | TA               | - 40 to +85<br>0 to +70 | €          |  |

| Operating Junction Temperature                        | TJ               | + 150                   | °C         |  |

| Storage Temperature Range                             | T <sub>stq</sub> | -65 to +150             | °C         |  |

ELECTRICAL CHARACTERISTICS (T<sub>A</sub> = 25° unless otherwise noted)

| Characteristic                                                                                                                                                                                                                                            | Symbol                              | LM285-1.2 |               |                  | LM385-1.2/LM385B-1.2 |                |                  |         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-----------|---------------|------------------|----------------------|----------------|------------------|---------|

|                                                                                                                                                                                                                                                           |                                     | Min       | Тур           | Max              | Min                  | Тур            | Max              | Unit    |

| Reverse Breakdown Voltage<br><sup>I</sup> Rmin ≤ <sup>I</sup> R ≤ 20 mA                                                                                                                                                                                   | V <sub>(BR)R</sub>                  |           |               |                  |                      |                |                  | V       |

| LM285-1.2/LM385B-1.2<br>LM385-1.2                                                                                                                                                                                                                         |                                     | 1.223     | 1.235<br>—    | 1.247            | 1.223<br>1.205       | 1.235<br>1.235 | 1.247<br>1.260   |         |

| Minimum Operating Current (TA = Tlow to Thigh Note 1)                                                                                                                                                                                                     | Rmin                                |           | 2.5           | 10               | _                    | 2.5            | 15               | μА      |

| Reverse Breakdown Voltage Change with Current $ R_{min}  \le  R  \le 1.0 \text{ mA}$ , $T_A = +25^{\circ}\text{C}$ $T_A = T_{low}$ to $T_{high}$ (Note 1) 1.0 $mA \le  R  \le 20 mA$ , $T_A = +25^{\circ}\text{C}$ $T_A = T_{low}$ to $T_{high}$ (Note 1) | ΔV <sub>(BR)</sub> /ΔI <sub>R</sub> | -<br>-    | <u>-</u><br>- | 1.0<br>1.5<br>10 | _<br>_<br>_          | _<br>_<br>_    | 1.0<br>1.5<br>20 | mV      |

| Reverse Dynamic Impedance<br>I <sub>R</sub> = 100 µA, T <sub>A</sub> = +25°C<br>T <sub>A</sub> = T <sub>low</sub> to T <sub>high</sub> (Note 1)                                                                                                           | Z                                   | _         | 0.2           | 0.6<br>1.5       | _                    | 0.4            | 25<br>1.0<br>1.5 | Ω       |

| Average Temperature Coefficient<br>10 $\mu$ A $\leq$ I <sub>R</sub> $\leq$ 20 mA, T <sub>A</sub> = T <sub>low</sub> to T <sub>high</sub> (Note 1)                                                                                                         | $\Delta V_{(BR)}/\Delta T$          | -         | 20            | _                | _                    | 20             | _                | ppm/°C  |

| Wideband Noise (RMS)<br>IR = 100 $\mu$ A, 10 Hz $\leq$ f $\leq$ 10 kHz                                                                                                                                                                                    | л                                   | _         | 60            | -                | _                    | 60             | _                | μV      |

| Long Term Stability<br>$I_R = 100 \mu A$ , $T_A = +25^{\circ}C \pm 0.1^{\circ}C$                                                                                                                                                                          | S                                   | -         | 20            | -                | _                    | 20             | _                | ppm/kHi |

#### **ELECTRICAL CHARACTERISTICS** (T<sub>A</sub> = 25° unless otherwise noted)

| Characteristic                                                                                                                                                                                                                                                   | Symbol                     | LM285-2.5 |          |                        | LM385-2.5/LM385B-2.5 |            |                        |         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------|----------|------------------------|----------------------|------------|------------------------|---------|

|                                                                                                                                                                                                                                                                  |                            | Min       | Тур      | Max                    | Min                  | Тур        | Max                    | Unit    |

| Reverse Breakdown Voltage 20 $\mu$ A $\leq$ I <sub>R</sub> $\leq$ 20 mA                                                                                                                                                                                          | V <sub>(BR)R</sub>         |           |          |                        |                      |            |                        | V       |

| LM285-2.5/LM385B-2.5<br>LM385-2.5                                                                                                                                                                                                                                |                            | 2.462     | 2.5<br>— | 2.538                  | 2.462<br>2.425       | 2.5<br>2.5 | 2.538<br>2.575         |         |

| Minimum Operating Current TA = T <sub>low</sub> to T <sub>high</sub> (Note 1)                                                                                                                                                                                    | IRmin                      | _         | 5.0      | 20                     | _                    | 5.0        | 20                     | μА      |

| Reverse Breakdown Voltage Change with Current $20~\mu A \leqslant I_R \leqslant 1.0~mA$ , $T_A = +25^{\circ}C$<br>$T_A = T_{low}$ to $T_{high}$ (Note 1) $1.0~mA \leqslant I_R \leqslant 20~mA$ , $T_A = +25^{\circ}C$<br>$T_A = T_{low}$ to $T_{high}$ (Note 1) | ΔV(BR)/<br>ΔI <sub>R</sub> |           |          | 1.0<br>1.5<br>10<br>20 | -<br>-<br>-          |            | 2.0<br>2.5<br>20<br>25 | mV      |

| Reverse Dynamic Impedance<br>I <sub>R</sub> = 100 μA, Τ <sub>A</sub> = +25°C<br>T <sub>A</sub> = T <sub>low</sub> to T <sub>high</sub> (Note 1)                                                                                                                  | Z                          | _         | 0.2      | 0.6<br>1.5             | _                    | 0.4        | 1.0                    | Ω       |

| Average Temperature Coefficient<br>$20 \mu A \le I_R \le 20 \text{ mA}$ , $T_A = T_{low}$ to $T_{high}$ (Note 1)                                                                                                                                                 | ΔV(BR)/<br>ΔT              | -         | 20       | _                      | -                    | 20         | _                      | ppm/°C  |

| Wideband Noise (RMS)<br>$I_R = 100 \mu A$ , 10 Hz $\leq f \leq 10 \text{ kHz}$                                                                                                                                                                                   | n                          | -         | 120      | _                      | _                    | 120        | -                      | μ٧      |

| Long Term Stability<br>I <sub>R</sub> = 100 μA, Τ <sub>Α</sub> = +25°C ±0.1°C                                                                                                                                                                                    | S                          | -         | 20       | _                      |                      | 20         |                        | ppm/kHF |

$<sup>\</sup>begin{split} T_{high} &= +85^{\circ}\text{C for LM285-1.2, LM285-2.5} \\ &= +70^{\circ}\text{C for LM385-1.2, LM385B-1.2, LM385-2.5, LM385B-2.5} \end{split}$

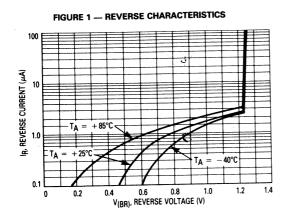

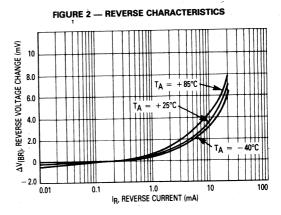

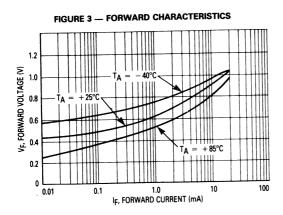

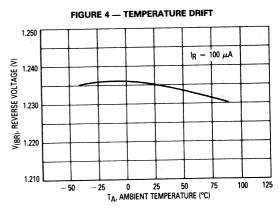

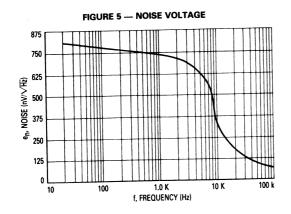

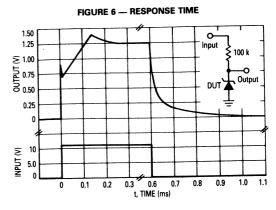

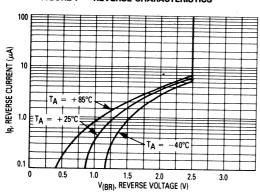

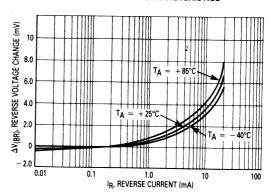

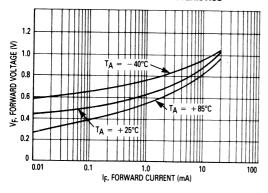

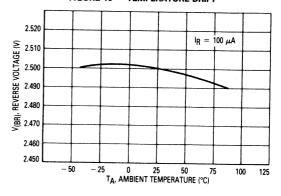

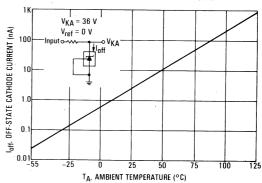

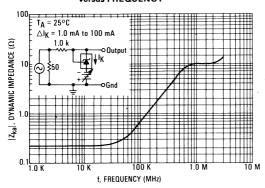

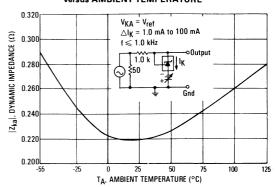

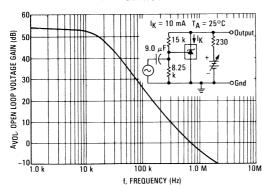

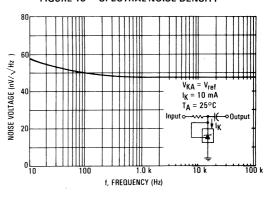

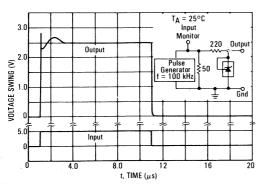

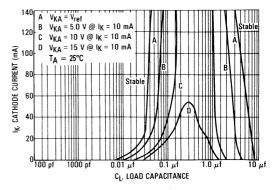

# TYPICAL PERFORMANCE CURVES FOR LM285-1.2/385-1.2/385B-1.2

# TYPICAL PERFORMANCE CURVES FOR LM285-2.5/385-2.5/385B-2.5

# FIGURE 8 — REVERSE CHARACTERISTICS

FIGURE 9 — FORWARD CHARACTERISTICS

FIGURE 10 — TEMPERATURE DRIFT

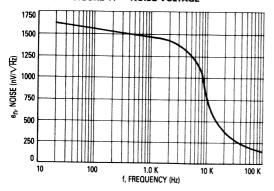

FIGURE 11 - NOISE VOLTAGE

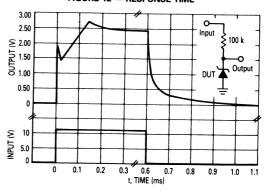

FIGURE 12 - RESPONSE TIME

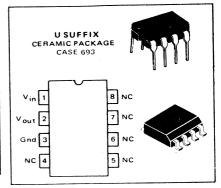

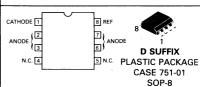

# MC1403,A MC1503,A

# LOW-VOLTAGE REFERENCE

A precision band-gap voltage reference designed for critical instrumentation and D/A converter applications. This unit is designed to work with Motorola MC1506, MC1508, and MC3510 D/A converters, and MC14433 A/D systems. Low temperature drift is a prime design consideration.

- Output Voltage = 2.5 V ± 25 mV

- Input Voltage Range = 4.5 V to 40 V

- Quiescent Current = 1.2 mA typ

- Output Current = 10 mA

- Temperature Coefficient = 10 ppm/<sup>O</sup>C typ

- Guaranteed Temperature Drift Specification

- Equivalent to AD580

- Standard 8-Pin DIP Package

### Typical Applications

- Voltage Reference for 8-12 Bit D/A Converters

- Low TC Zener Replacement

- High Stability Current Reference

- Voltmeter System Reference

# PRECISION LOW-VOLTAGE REFERENCE

LASER TRIMMED SILICON MONOLITHIC INTEGRATED CIRCUIT

# MAXIMUM RATINGS (TA = 25°C unless otherwise noted.)

| Rating                                                      | Symbol           | Value                   | Unit |

|-------------------------------------------------------------|------------------|-------------------------|------|

| Input Voltage                                               | ٧ı               | 40                      | V .  |

| Storage Temperature                                         | T <sub>stg</sub> | -65 to 150              | °C   |

| Junction Temperature                                        | Tj               | +175                    | °C   |

| Operating Ambient Temeprature Range<br>MC1503,A<br>MC1403,A | ТА               | -55 to +125<br>0 to +70 | °C   |

### ORDERING INFORMATION Temperature **Package** Device Range -55 to +125 °C Ceramic DIP MC1503U Ceramic DIP -55 to +125 °C MC1503AU 0 to +70°C Ceramic DIP MC1403U Ceramic DIP 0 to + 70°C MC1403AU

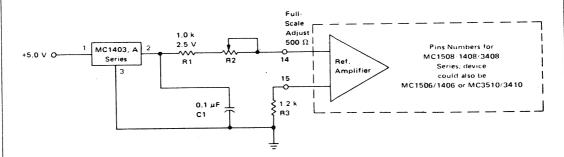

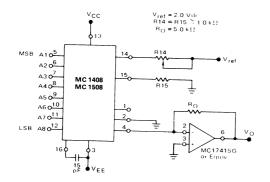

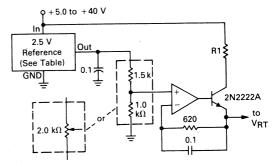

# FIGURE 1 - A REFERENCE FOR MOTOROLA MONOLITHIC D/A CONVERTERS

# PROVIDING THE REFERENCE CURRENT FOR MOTOROLA MONOLITHIC D/A CONVERTERS

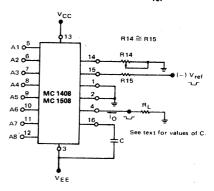

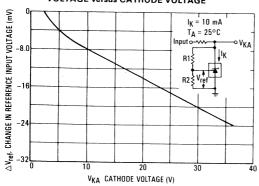

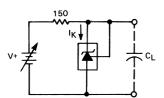

The MC1403/1503 makes an ideal reference for the Motorola monolithic D/A converters. The MC1406/1506, MC1408/1508, MC3410/3510 and MC3408 D/A converters all require a stable current reference of nominally 2.0 mA. This can be easily obtained from the MC1403/1503 with the addition of a series resistor, R1. A variable resistor, R2, is

recommended to provide means for full-scale adjust on the D/A converter.

The resistor R3 improves temperature performance by matching the impedance on both inputs of the D/A reference amplifier. The capacitor decouples any noise present on the reference line. It is essential if the D/A converter is located any appreciable distance from the reference.

A single MC1403/1503 reference can provide the required current input for up to five of the monolithic D/A converters.

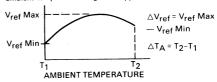

**ELECTRICAL CHARACTERISTICS** ( $V_I$  = 15 V,  $T_A$  = 25 $^{\rm o}$ C unless otherwise noted.)

| Characteristic                                           | Symbol              | Min   | Тур      | Max        | Unit                |

|----------------------------------------------------------|---------------------|-------|----------|------------|---------------------|

| Output Voltage<br>(IO = 0 mA)                            | v <sub>o</sub>      | 2.475 | 2.50     | 2.525      | V                   |

| Temperature Coefficient of Output Voltage MC1503         | Δν <sub>Ο</sub> /ΔΤ |       |          |            | ppm/ <sup>O</sup> C |

| MC1503A                                                  |                     | _     | _        | 55<br>25   |                     |

| MC1403<br>MC1403A                                        |                     | _     | 10<br>10 | 40<br>25   |                     |

| Output Voltage Change (over specified temperature range) | ΔVO                 |       | 10       | 25         | m∨                  |

| MC1503<br>MC1503A } -55°C to +125°C                      |                     | -     | _        | 25<br>11   |                     |

| MC1403 } 0°C to +70°C                                    |                     | -     | _        | 7.0<br>4.4 |                     |

| Line Regulation<br>(15 V < V <sub>I</sub> < 40 V)        | Reg <sub>in</sub>   | -     | 1.2      | 4.5        | mV                  |

| (4.5 V < V <sub>I</sub> < 15 V)                          |                     |       | 0.6      | 3.0        |                     |

| Load Regulation (0 mA < I <sub>O</sub> < 10 mA)          | Regload             | -     | _        | 10         | mV                  |

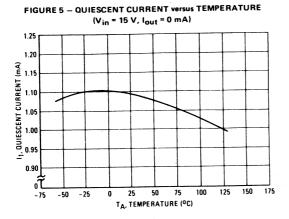

| Quiescent Current<br>(I <sub>O</sub> = 0 mA)             | 11                  | -     | 1.2      | 1.5        | mA                  |

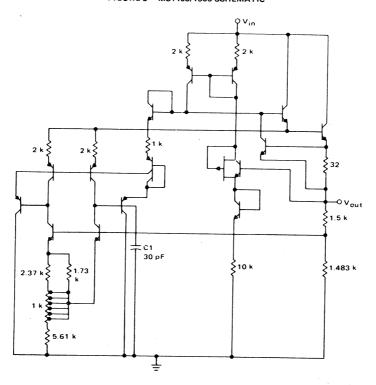

FIGURE 2 - MC1403/1503 SCHEMATIC

FIGURE 3 – TYPICAL CHANGE IN Vout versus Vin (NORMALIZED TO Vin = 15 V @ T<sub>C</sub> = 25°C)

10 25°C

10 20 30 40 50

Vin. INPUT VOLTAGE (VOLTS)

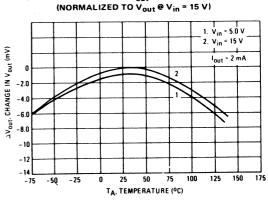

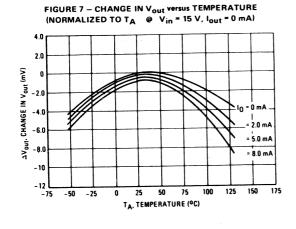

FIGURE 4 - CHANGE IN OUTPUT VOLTAGE

FIGURE 6 - CHANGE IN Vout versus TEMPERATURE

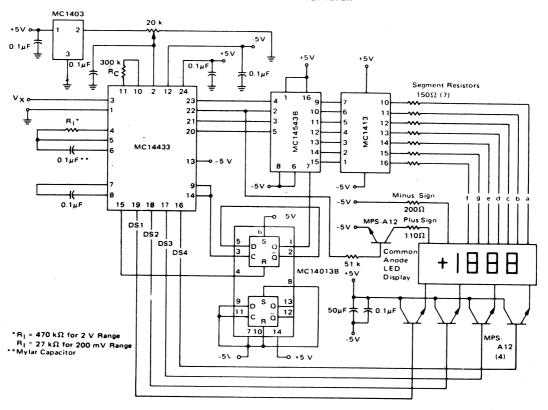

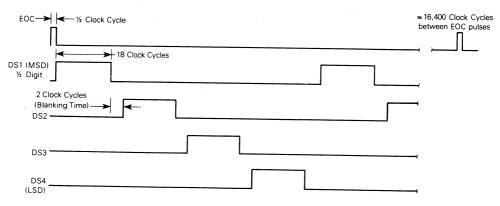

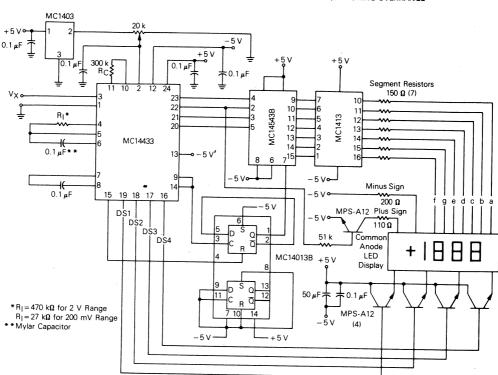

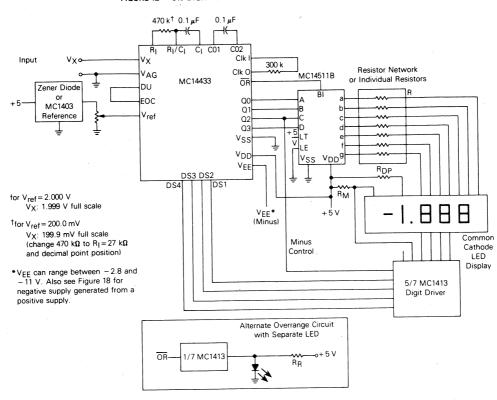

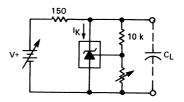

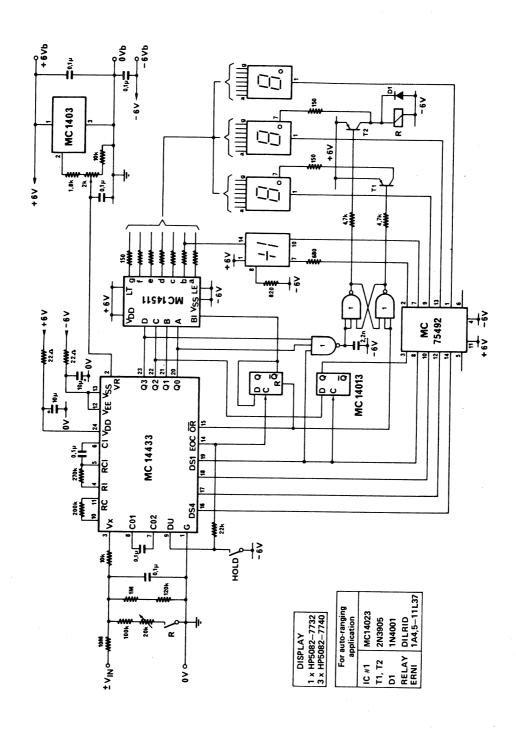

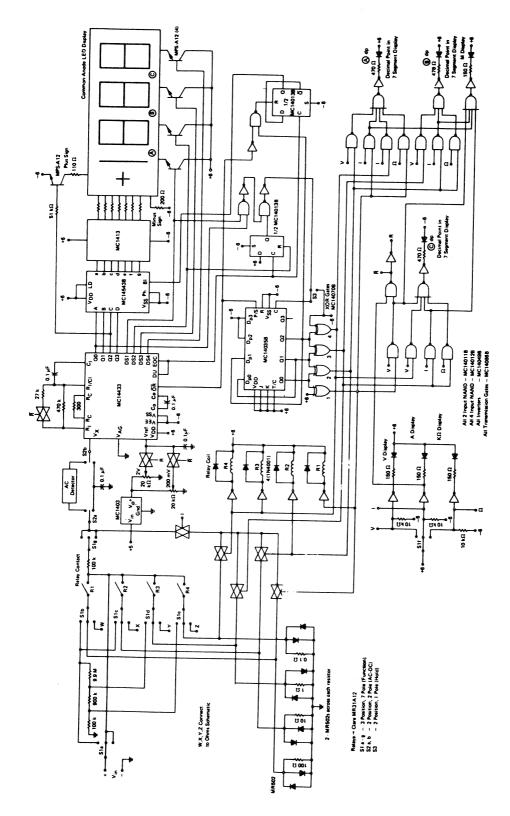

# 3-1/2-DIGIT VOLTMETER – COMMON ANODE DISPLAYS, FLASHING OVERRANGE

An example of a 3-1/2-digit voltmeter using the MC14433 is shown in the circuit diagram of Figure 8. The reference voltage for the system uses an MC1403 2.5 V reference IC. The full scale potentiometer can calibrate for a full scale of 199.9 mV or 1.999 V. When switching from 2 V to 200 mV operation, R<sub>1</sub> is also changed, as shown on the diagram.

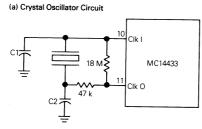

When using RC equal to 300 k $\Omega$ , the clock frequency for the system is about 66 kHz. The resulting conversion time is approximately 250 ms.

When the input is overrange, the display flashes on and off. The flashing rate is one-half the conversion rate.

This is done by dividing the EOC pulse rate by 2 with 1/2 MC14013B flip-flop and blanking the display using the blanking input of the MC14543B.

The display uses an LED display with common anode digit lines driven with an MC14543B decoder and an MC1413 LED driver. The MC1413 contains 7 Darlington transistor drivers and resistors to drive the segments of the display. The digit drive is provided by four MPS-A12 Darlington transistors operating in an emitter-follower configuration. The MC14543B, MC14013B and LED displays are referenced to VEE via pin 13 of the MC14433. This places the full power supply voltage across the display. The current for the display may be adjusted by the value of the segment resistors shown as 150 ohms in Figure 8.

# FIGURE 8 - 3-1/2-DIGIT VOLTMETER

# Specifications and Applications Information

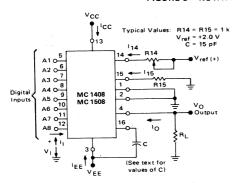

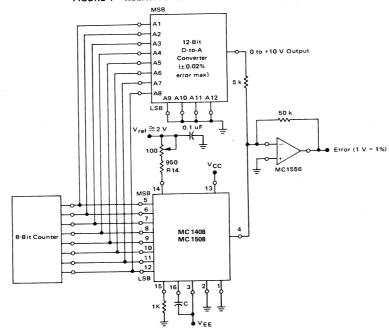

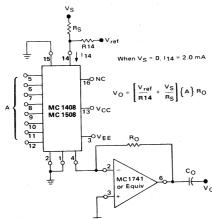

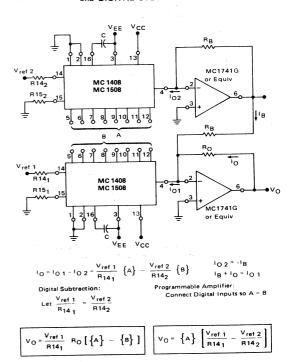

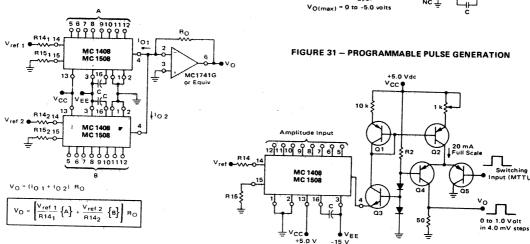

# EIGHT-BIT MULTIPLYING DIGITAL-TO-ANALOG CONVERTER

. . . designed for use where the output current is a linear product of an eight-bit digital word and an analog input voltage.

- Eight-Bit Accuracy Available in Both Temperature Ranges Relative Accuracy: ±0.19% Error maximum (MC1408L8, MC1408P8, MC1508L8)

- Fast Settling Time 300 ns typical

- Noninverting Digital Inputs are MTTL and CMOS Compatible

- Output Voltage Swing +0.4 V to -5.0 V

- High-Speed Multiplying Input Slew Rate 4.0 mA/μs

- Standard Supply Voltages: +5.0 V and -5.0 V to -15 V

# MC1408 MC1508

EIGHT-BIT MULTIPLYING DIGITAL-TO-ANALOG CONVERTER

SILICON MONOLITHIC INTEGRATED CIRCUIT

# FIGURE 1 – D-to-A TRANSFER CHARACTERISTICS (YE) (O00000000) (O00000000) (INPUT DIGITAL WORD

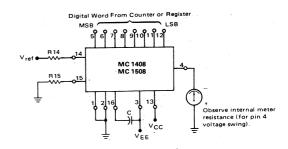

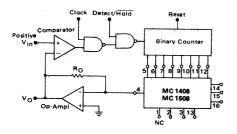

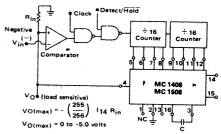

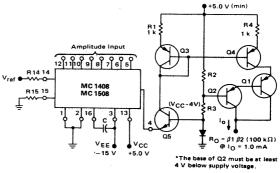

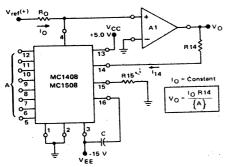

# TYPICAL APPLICATIONS

- Tracking A-to-D Converters

- Successive Approximation A-to-D Converters

- 2 1/2 Digit Panel Meters and DVM's

- Waveform Synthesis

- Sample and Hold

- Peak Detector

- Programmable Gain and Attenuation

- CRT Character Generation

- Audio Digitizing and Decoding

- Programmable Power Supplies

- Analog-Digital Multiplication

- Digital-Digital Multiplication

- Analog-Digital Division

- Digital Addition and Subtraction

- Speech Compression and Expansion

- Stepping Motor Drive

DS 9238 R1

# MAXIMUM RATINGS (T<sub>A</sub> = +25°C unless otherwise noted.)

| Rating                                          | Symbol                              | Value                            | Unit |

|-------------------------------------------------|-------------------------------------|----------------------------------|------|

| Power Supply Voltage                            | V <sub>CC</sub><br>V <sub>EE</sub>  | +5.5<br>-16.5                    | Vdc  |

| Digital Input Voltage                           | V <sub>5</sub> thru V <sub>12</sub> | 0 to +5.5                        | Vdc  |

| Applied Output Voltage                          | v <sub>o</sub>                      | +0.5,-5.2                        | Vdc  |

| Reference Current                               | 114                                 | 5.0                              | mA   |

| Reference Amplifier Inputs                      | V <sub>14</sub> ,V <sub>15</sub>    | V <sub>CC</sub> ,V <sub>EE</sub> | Vdc  |

| Operating Temperature Range<br>MC1508<br>MC1408 | т <sub>А</sub>                      | -55 to +125<br>0 to +75          | °C   |

| Storage Temperature Range                       | T <sub>stg</sub>                    | 65 to +150                       | °C   |

ELECTRICAL CHARACTERISTICS ( $V_{CC}$  = +5.0 Vdc,  $V_{EE}$  = -15 Vdc,  $\frac{V_{ref}}{R_{14}}$  = 2.0 mA, MC1508L8:  $T_A$  = -55°C to +125°C. MC1408L Series:  $T_A$  = 0 to +75°C unless otherwise noted. All digital inputs at high logic level.)

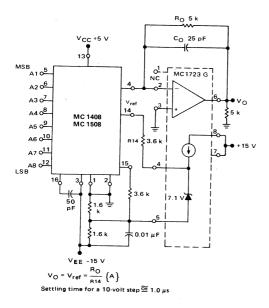

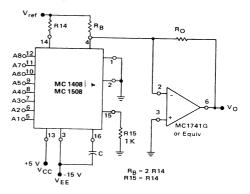

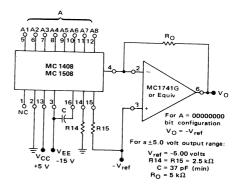

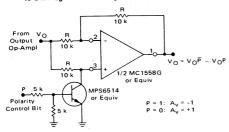

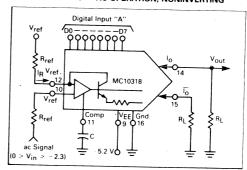

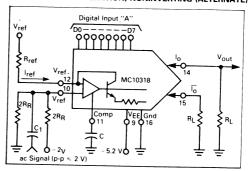

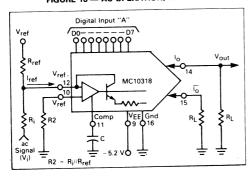

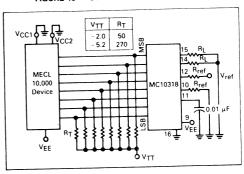

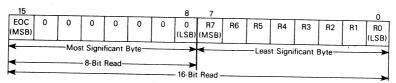

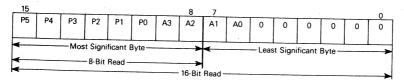

| Characteristic                                                                                                                      | Figure      | Symbol                               | Min          | Тур           | Max               | Unit                     |